【三維晶片集成與封裝技術】

內容簡介

本書系統地討論了用於電子、光電子和MEMS器件的2.5D、3D,以及3D IC集成和封裝技術的最新進展和未來可能的演變趨勢,同時詳盡地討論了IC的3D集成和封裝關鍵技術中存在的主要工藝問題和可能的解決方案。 通過介紹半導體產業中IC按照摩爾定律的發展以及演變的歷史,闡述3D集成和封裝的優勢和挑戰,結合當前3D集成關鍵技術的發展重點討論TSV制程與模型、晶圓减薄與薄晶圓在封裝組裝過程中的拿持晶圓鍵合科技、3D堆疊的微凸點製造與組裝科技、3D Si集成、2.5D/3D IC集成和採用無源轉接板的3D IC集成、 2.5D/3D IC集成的熱管理科技、封裝基板科技,以及記憶體、LED、MEMS、CIS 3D IC集成等關鍵技術問題,最後討論3D IC封裝技術。

本書適合從事電子、光電子、MEMS等器件3D集成的工程師、科研人員和科技管理人員閱讀,也可以作為高等院校相關專業高年級大學生和研究生的教材和參考書。

作者簡介

原書作者簡介

劉漢誠(John H. Lau)博士是電子、光電、LED、CIS和MEMS元件和系統方面設計、分析、資料、工藝、製造、鑒定、可靠性、測試和熱管理等領域的著名專家,特別是在焊接力學和製造、符合RoHS的產品、SMT、扇入和扇出倒裝晶片WLP、TSV,以及其他用於IC的3D集成和SiP科技方面有著超高造詣。

劉博士擁有40多年的集成電路研發和製造經驗,撰寫或合作撰寫了超過425篇科技論文,發佈或正在申請的專利多達30餘項,並在全球範圍內進行了290多次講座/研討會/主題演講。 他撰寫或合著了18部關於IC的3D集成、TSV的3D集成、先進MEMS封裝、IC的2D和3D互連可靠性、倒裝晶片WLP、面陣列封裝、高密度PCB、SMT、DCA、無鉛資料、焊接、製造和焊點可靠性等方面的教材。

目錄

譯者序

原書前言

第1章電晶體IC封裝的3D集成1

1.1引言1

1.2 3D集成2

1.3 3D IC封裝4

1.4 3D Si集成5

1.5 3D IC集成7

1.5.1混合記憶體立方7

1.5.2寬I/O DRAM和寬I/O 29

1.5.3高頻寬記憶體9

1.5.4寬I/O記憶體(或邏輯對邏輯)11

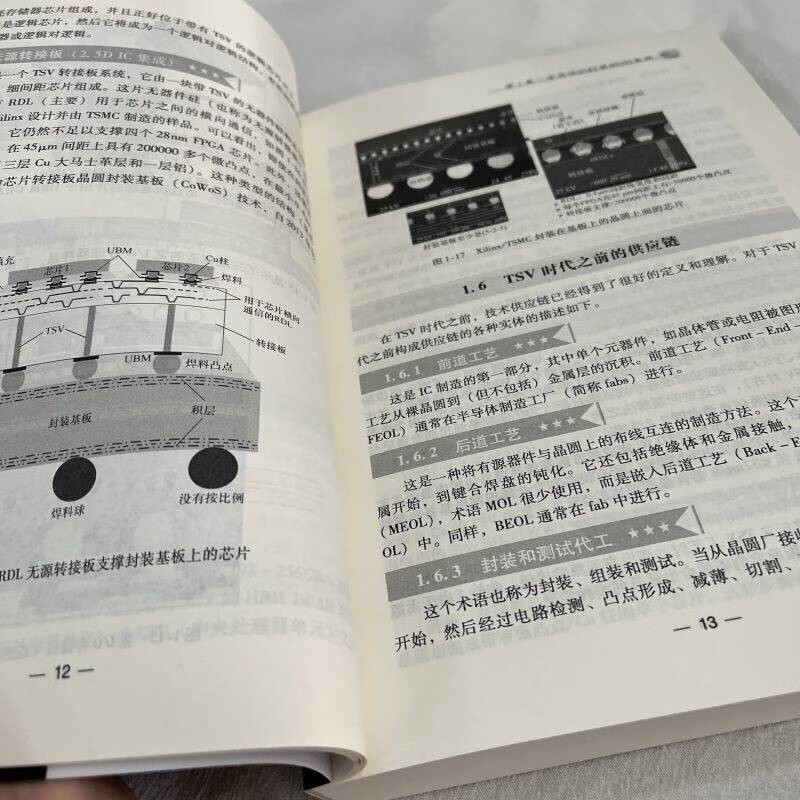

1.5.5無源轉接板(2.5D IC集成)12

1.6 TSV時代之前的供應鏈13

1.6.1前道工藝13

1.6.2後道工藝13

1.6.3封裝和測試代工13

1.7 TSV時代的供應鏈——誰製造TSV? 14

1.7.1TSV通過先通孔工藝製造14

1.7.2TSV通過中通孔工藝製造14

1.7.3TSV通過後通孔(從正面)工藝製造14

1.7.4TSV通過後通孔(從背面)工藝製造14

1.7.5無源TSV轉接板怎麼樣? 14

1.7.6誰想為無源轉接板製造TSV? 15

1.7.7總結和建議15

1.8 TSV時代的供應鏈——誰負責MEOL、組裝和測試? 15

1.8.1寬I/O記憶體(面對背)的中通孔TSV制造技術15

1.8.2寬I/O記憶體(面對面)的中通孔TSV制造技術16

1.8.3寬I/O DRAM的中通孔TSV制造技術17

1.8.4帶有TSV/RDL無源轉接板的2.5D IC集成17

1.8.5總結和建議19

1.9採用TSV科技的CMOS圖像感測器19

1.9.1東芝的DynastronTM19

1.9.2意法半導體VGA CIS攝像模塊20

1.9.3三星的S5K4E5YX BSI圖像感測器20

1.9.4東芝的HEW4 BSITCM5103PL圖像感測器21

1.9.5Nemotek的CIS22

1.9.6索尼ISX014堆疊式攝像感測器23

1.10帶有TSV的MEMS23

1.10.1意法半導體的MEMS慣性感測器23

1.10.2Discera的MEMS諧振器24

1.10.3Avago的FBAR MEMS濾波器24

1.11參考文獻26

第2章矽通孔建模和測試31

2.1引言31

2.2 TSV的電學建模31

2.2.1通用TSV結構的解析模型和方程31

2.2.2TSV模型的頻域驗證34

2.2.3TSV模型的時域驗證38

2.2.4TSV的電學設計指南38

2.2.5總結和建議41

2.3 TSV的熱學建模42

2.3.1 Cu填充的TSV等效熱導率選取42

2.3.2TSV單元的熱學特性45

2.3.3 Cu填充的TSV等效熱導率方程48

2.3.4 TSV等效熱導率方程的驗證52

2.3.5總結和建議54

2.4 TSV的機械建模和測試54

2.4.1Cu填充TSV和周圍Si之間的TEM55

2.4.2製造中Cu脹出實驗結果56

2.4.3熱衝擊迴圈下的Cu脹出60

2.4.4Cu填充的TSV排除區域62

2.4.5總結和建議65

2.5參考文獻67

第3章用於薄晶圓拿持和應力量測的應力感測器70

3.1引言70

3.2壓阻式應力感測器的設計和製造70

3.2.1壓阻式應力感測器的設計70

3.2.2應力感測器的製造71

3.2.3總結和建議75

3.3應力感測器在薄晶圓拿持中的應用76

3.3.1壓阻式應力感測器的設計、製造和校準76

3.3.2矽片减薄後的應力量測80

3.3.3總結和建議81

3.4應力感測器在晶圓凸點製造中的應用81

3.4.1UBM製造後的應力82

3.4.2幹膜工藝後的應力84

3.4.3焊料凸點制造技術後的應力85

3.4.4總結和建議85

3.5應力感測器在嵌入式超薄晶片跌落試驗中的應用87

3.5.1測試板和製造87

3.5.2實驗裝置和流程88

3.5.3原位應力量測結果89

3.5.4可靠性測試91

3.5.5總結和建議92

3.6參考文獻93

第4章封裝基板科技96

4.1引言96

4.2用於倒裝晶片3D IC集成的帶有積層的封裝基板96

4.2.1表面層壓電路科技96

4.2.2帶有積層的封裝基板的發展趨勢98

4.2.3總結與建議99

4.3無覈心封裝基板99

4.3.1無覈心封裝基板的優缺點99

4.3.2採用無覈心基板替代Si轉接板100

4.3.3無覈心基板翹曲問題及解決方法102

4.3.4總結與建議105

4.4具有積層的封裝基板的新進展105

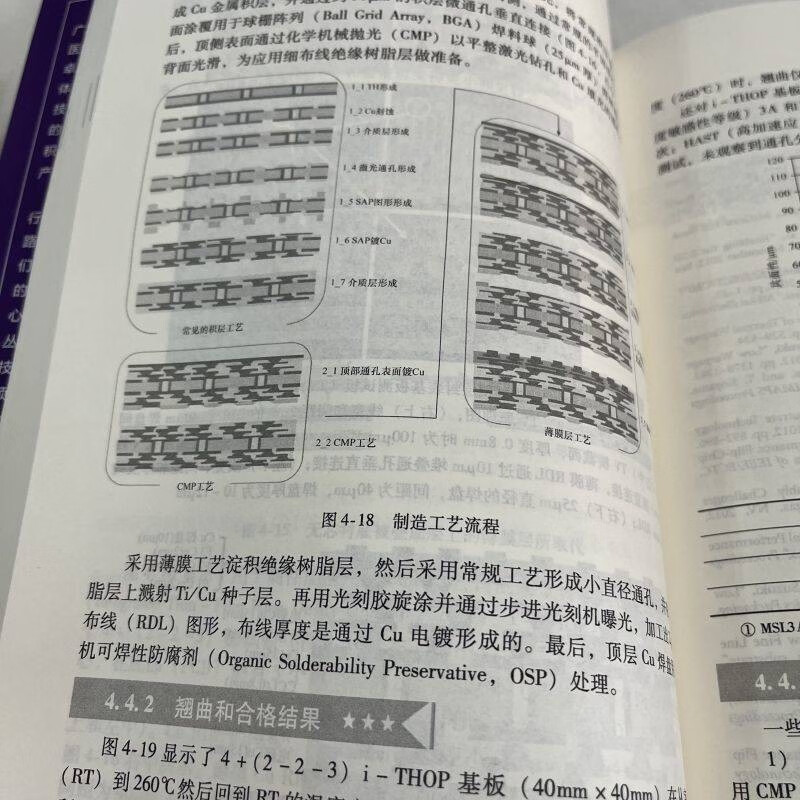

4.4.1封裝基板積層頂部的薄膜層106

4.4.2翹曲和合格結果108

4.4.3總結與建議109

4.5參考文獻110

第5章微凸點:製造、組裝和可靠性112

5.1引言112

5.2 25 μ m間距微凸點的製造、裝配和可靠性112

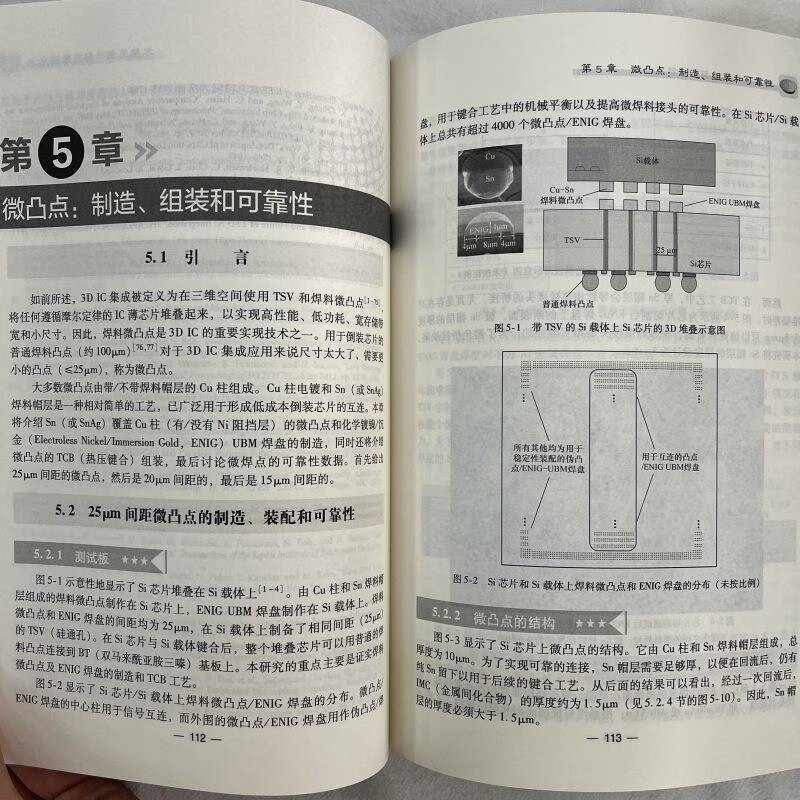

5.2.1測試板112

5.2.2微凸點的結構113

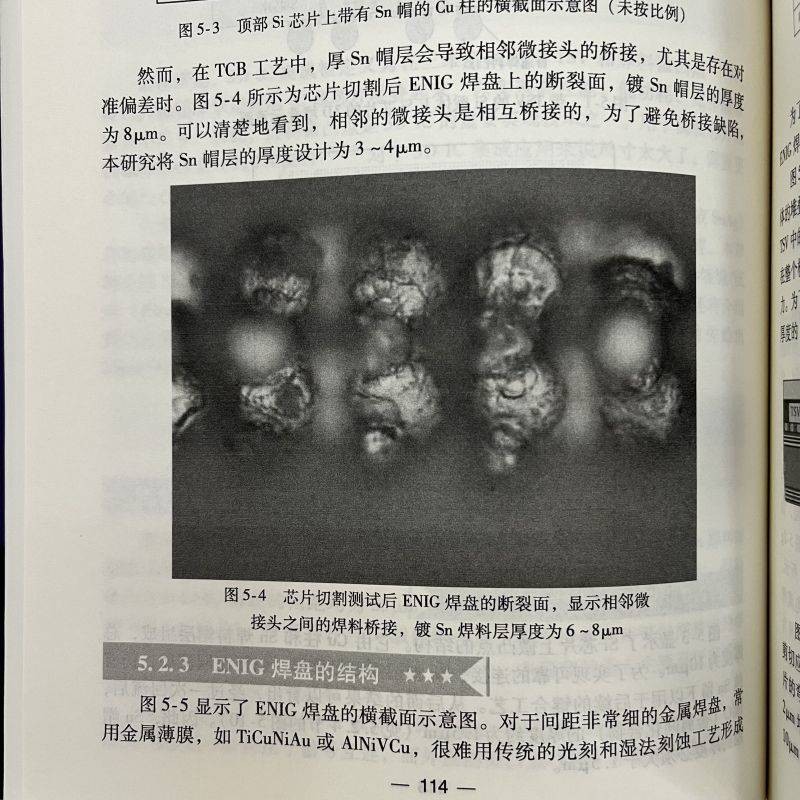

5.2.3ENIG焊盤的結構114

5.2.425 μ m間距微凸點的製造116

5.2.5在Si載體上製造ENIG焊盤118

5.2.6熱壓鍵合組裝119

5.2.7底部填充的評估123

5.2.8可靠性評估124

5.2.9總結和建議125

5.320 μ m間距的微凸點製造、組裝和可靠性125

5.3.1測試板125

5.3.2測試板裝配126

5.3.3熱壓鍵合微接頭的形成127

5.3.4微間隙填充128

5.3.5可靠性測試129

5.3.6可靠性測試結果與討論130

5.3.7微接頭的失效機理133

5.3.8總結與建議136

5.4 15 μ m間距微凸點的製造、裝配和可靠性136

5.4.1測試板的微凸點和UBM焊盤136

5.4.2組裝138

5.4.3採用CuSn焊料微凸點與ENIG焊盤組裝139

5.4.4採用CuSn焊料微凸點的組裝139

5.4.5底部填充的評估139

5.4.6總結與建議139

5.5參考文獻140

第6章3D Si集成145

6.1引言145

6.2電子工業145

6.3摩爾定律和超越摩爾定律147

6.4 3D集成的起源148

6.5 3D Si集成的概述與展望149

6.5.13D Si集成的鍵合方法149

6.5.2Cu-Cu(W2W)鍵合151

6.5.3Cu-Cu(W2W)後退火鍵合152

6.5.4Cu-Cu(W2W)常溫鍵合152

6.5.5SiO2-SiO2(W2W)鍵合153

6.5.6W2W鍵合的一些注意事項157

6.63D Si集成科技面臨的挑戰157

6.73D Si集成EDA工具面臨的挑戰157

6.8總結和建議158

6.9參考文獻160

第7章2.5D3D IC集成163

7.1引言163

7.23D IC集成的TSV工藝164

7.2.1晶片上的微通孔164

7.2.2先通孔工藝164

7.2.3中通孔工藝164

7.2.4正面後通孔工藝166

7.2.5背面後通孔工藝166

7.2.6總結與建議167

7.3 3D IC集成的潜在應用167

7.4記憶體晶片堆疊168

7.4.1晶片168

7.4.2潜在產品168

7.4.3組裝工藝170

7.5寬I/O記憶體或邏輯-邏輯堆疊170

7.5.1晶片170

7.5.2潜在產品171

7.5.3組裝工藝173

7.6寬I/O DRAM或混合記憶體立方175

7.6.1晶片175

7.6.2潜在產品177

7.6.3組裝工藝178

7.7寬I/O 2和高頻寬記憶體179

7.8寬I/O介面(2.5D IC集成)180

7.8.1TSV/RDL無源轉接板的實際應用182

7.8.2轉接板的製造183

7.8.3TSV的製造183

7.8.4RDL的製造184

7.8.5RDL的製造——聚合物/電鍍Cu方法185

7.8.6RDL的製造——Cu大馬士革方法187

7.8.7Cu大馬士革方法中接觸式對準光刻機的注意事項190

7.8.8背面加工和組裝190

7.8.9總結和建議191

7.9薄晶圓拿持193

7.9.1常規的薄晶圓拿持方法193

7.9.2TI的TSV-WCSP集成工藝194

7.9.3TSMC的聚合物薄晶圓拿持194

7.9.4TSMC無臨時鍵合和剝離的薄晶圓拿持195

7.9.5帶有散熱晶圓的薄晶圓拿持196

7.9.6總結與建議196

7.10參考文獻199

第8章採用無源轉接板的3D IC集成203

8.1引言203

8.2採用TSV/RDL轉接板的3D IC集成203

8.3雙面貼附晶片的TSV/RDL轉接板204

8.3.1結構204

8.3.2熱分析——邊界條件206

8.3.3熱分析——TSV的等效模型206

8.3.4熱分析——焊料凸點/底部填充的等效模型207

8.3.5熱分析結果207

8.3.6熱機械分析——邊界條件210

8.3.7資料效能的熱機械分析——資料特性210

8.3.8熱機械分析結果211

8.3.9TSV的製造214

8.3.10採用頂部RDL的轉接板的製造217

8.3.11頂部帶RDL Cu填充的轉接板的TSV露出217

8.3.12採用底部RDL的轉接板的製造218

8.3.13轉接板的無源電學特性表徵221

8.3.14終組裝222

8.3.15總結和建議225

8.4兩側帶有晶片的TSV轉接板226

8.4.1結構226

8.4.2熱分析——資料特性227

8.4.3熱分析——邊界條件228

8.4.4熱分析——結果與討論228

8.4.5熱機械分析——資料特性231

8.4.6熱機械分析——邊界條件231

8.4.7熱機械分析——結果與討論232

8.4.8轉接板製造235

8.4.9微凸點晶圓的凸點製造238

8.4.10終組裝240

8.4.11總結和建議242

8.5用於3D IC集成的低成本TSH轉接板244

8.5.1新設計244

8.5.2電學模擬245

8.5.3測試板247

8.5.4帶UBM/焊盤和Cu柱的頂部晶片249

8.5.5帶有UBM/焊盤/焊料的底部晶片250

8.5.6TSH轉接板製造252

8.5.7終組裝253

8.5.8可靠性評估256

8.5.9總結和建議258

8.6參考文獻260

第9章2.5D/3D IC集成的熱管理262

9.1引言262

9.2設計理念262

9.3新設計263

9.4熱分析的等效模型264

9.5頂部帶晶片/散熱片以及底部帶晶片的轉接板265

9.5.1結構265

9.5.2資料特性266

9.5.3邊界條件267

9.5.4模擬結果267

9.6頂部帶有晶片/散熱片以及底部帶有晶片/熱沉的轉接板268

9.6.1結構與邊界條件268

9.6.2模擬結果268

9.7頂部帶有四個帶散熱片晶片的轉接板270

9.7.1結構270

9.7.2邊界條件270

9.7.3模擬結果272

9.7.4總結和建議274

9.8 2.5D IC和3D IC集成之間的熱效能274

9.8.1結構274

9.8.2有限元模型276

9.8.3資料特性和邊界條件276

9.8.4低功率應用的模擬結果277

9.8.5高功率應用的模擬結果277

9.8.6總結和建議279

9.9帶有嵌入式微通道的TSV轉接板的熱管理系統279

9.9.1結構279

9.9.2轉接器280

9.9.3熱交換器281

9.9.4載板282

9.9.5系統集成283

9.9.6壓降的理論分析283

9.9.7實驗過程285

9.9.8結果和討論286

9.9.9總結和建議289

9.10參考文獻290

第10章嵌入式3D混合集成292

10.1引言292

10.2光電子產品的發展趨勢292

10.3舊設計——PCB上使用光波導的高頻數據互連293

10.3.1聚合物光波導294

10.3.2模擬——光耦合模型296

10.3.3模擬——系統連接設計301

10.3.4OECB組裝302

10.3.5OECB的量測結果303

10.3.6總結和建議305

10.4舊設計——嵌入式板級光互連306

10.4.1聚合物波導的製造306

10.4.245°微鏡的製造307

10.4.3OECB的組裝工藝313

10.4.4垂直光通道制造技術313

10.4.5終組裝314

10.4.6總結和建議314

10.5新設計316

10.6一個嵌入式3D混合集成設計實例317

10.6.1光學設計、分析和結果318

10.6.2熱設計、分析和結果320

10.6.3機械設計、分析和結果322

10.6.4總結和建議325

10.7帶有應力消除間隙的半嵌入式TSV轉接板325

10.7.1設計理念325

10.7.2問題定義326

10.7.3工作條件下的半嵌入式TSV轉接板327

10.7.4環境條件下的半嵌入式TSV轉接板331

10.7.5總結和建議333

10.8參考文獻334

第11章LED與IC的3D集成337

11.1引言337

11.2Haitz定律的現狀和展望337

11.3LED已經走過了漫長的道路340

11.4LED產品的四個關鍵部分342

11.4.1LED襯底外延澱積342

11.4.2LED器件製造343

11.4.3LED封裝組裝與測試343

11.4.4 LED終產品組裝343

11.4.5 LED產品的展望346

11.5 LED與IC的3D集成347

11.5.1HP FCLED和薄膜FCLED347

11.5.2LED與IC的3D集成封裝349

11.5.3LED與IC的3D集成制造技術350

11.5.4總結和建議355

11.6 IC和LED的2.5D集成356

11.6.1基於帶有腔體以及銅填充TSV的Si基板的LED封裝356

11.6.2基於腔體和TSV Si基板的LED封裝360

11.6.3LED晶圓級封裝364

11.6.4總結和建議368

11.7 LED與IC 3D集成的熱管理368

11.7.1新設計370

11.7.2IC和LED的3D集成:一個設計示例371

11.7.3邊界值問題371

11.7.4模擬結果(通道高度=700 μ m)372

11.7.5模擬結果(通道高度=350 μ m)376

11.7.6總結和建議377

11.8參考文獻378

第12章MEMS與IC的3D集成381

12.1引言381

12.2 MEMS封裝381

12.3 MEMS與IC的3D集成383

12.3.1帶有橫向電饋通的MEMS與IC的3D集成383

12.3.2ASIC中帶有垂直電饋通的MEMS和IC的3D集成384

12.3.3封裝帽中帶有垂直電饋通的MEMS與IC的3D集成386

12.3.4在ASIC上帶有TSV的MEMS與IC的3D集成386

12.3.5MEMS與IC的2.5D/2.25D集成386

12.4 MEMS與IC 3D集成的組裝工藝387

12.4.1帶有橫向電饋通的MEMS和IC的3D集成389

12.4.2ASIC中帶垂直電饋通的MEMS和IC的3D集成389

12.4.3在封裝帽中帶有垂直電貫通的MEMS和IC的3D集成391

12.4.4關於情形10:一個真實的MEMS和IC的3D集成391

12.4.5總結和建議392

12.5採用低溫焊料鍵合的3D MEMS封裝392

12.5.1不同晶片尺寸的IC和MEMS 3D集成393

12.5.2帽晶圓中的腔體和TSV395

12.5.3MEMS晶片與ASIC晶圓鍵合(C2W)397

12.5.4帶有MEMS晶片的ASIC晶圓與帽晶圓的鍵合(W2W)399

12.5.5總結與建議400

12.6 MEMS先進封裝的新發展401

12.6.1用於RF MEMS晶圓級封裝的TSV科技401

12.6.2TSV與金屬鍵合科技實現RF-MEMS的零級封裝405

12.6.3基於帶Cu填充的TSV Si轉接板晶圓的MEMS封裝409

12.6.4基於FBAR振盪器的晶圓級封裝409

12.6.5總結與建議412

12.7參考文獻414

第13章CIS與IC的3D集成416

13.1引言416

13.2FI-CIS和BI-CIS 416

13.33D CIS和IC堆疊418

13.3.1結構418

13.3.2CIS點數晶圓和邏輯IC晶圓的製造418

13.43D CIS和IC集成420

13.4.1結構420

13.4.2輔助處理器晶圓製造工藝流程421

13.4.3CIS晶圓的製造工藝流程422

13.4.4終組裝423

13.5總結和建議424

13.6參考文獻425

第14章3D IC封裝426

14.1引言426

14.2採用引線鍵合的晶片堆疊426

14.2.1Au線426

14.2.2Cu線和Ag線426

14.3疊層封裝428

14.3.1引線鍵合PoP 428

14.3.2倒裝晶片PoP 428

14.3.3倒裝晶片封裝上的引線鍵合封裝428

14.3.4iPhone 5s中的PoP 429

14.4晶圓級封裝431

14.4.1扇入晶圓級封裝431

14.4.2晶片-晶片的3D晶圓級封裝432

14.5扇出eWLP 435

14.5.1扇出eWLP 435

14.5.23D eWLP——雙晶片堆疊437

14.5.33D eWLP——在eWLP上的晶片(面對面)438

14.5.43D eWLP——在eWLP上的晶片(面對背)438

14.5.53D eWLP——在eWLP上的封裝438

14.5.63D eWLP——在eWLP上的eWLP439

14.6嵌入式板級封裝440

14.6.1優勢和劣勢440

14.6.2不同晶片嵌入工藝441

14.6.3SiP剛性基板中嵌入的晶片442

14.6.4SiP柔性基板中嵌入的3D晶片442

14.6.5SiP柔性基板中嵌入的3D晶片堆疊443

14.7總結和建議444

14.8參考文獻444

-------------------------------------------------------

【積體電路設計中的電源管理科技】

內容簡介

《集成電路設計中的電源管理技術》主要針對低壓和高壓電源管理電路設計進行了詳細討論。 《集成電路設計中的電源管理技術》力求簡化電路模型的數學分析,重點研究電源管理電路的功能和實現。 《集成電路設計中的電源管理技術》中包含了大量電路示意圖,以幫助讀者理解電源管理電路的基本原理和工作方式。 在具體內容方面,《集成電路設計中的電源管理技術》分章介紹了低壓和高壓器件、低壓差線性穩壓器設計、電壓模式和電流模式開關電源穩壓器、基於紋波的控制科技、單電感多輸出轉換器、基於開關的電池充電器以及能量收集系統等方面的內容。

《集成電路設計中的電源管理技術》內容詳實、實例豐富,可作為高等院校電子科學與科技、電子資訊工程、微電子、集成電路工程等專業高年級大學生和碩士研究生的課程教材,亦可作為從事集成電路、系統級設計,以及電源管理晶片設計和應用的工程技術人員的參攷書籍。

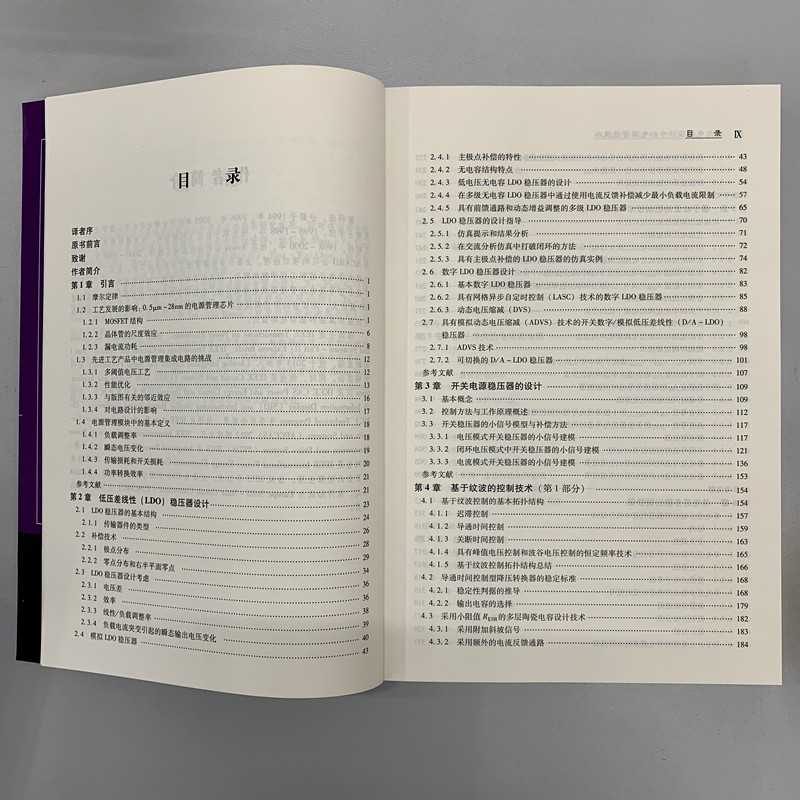

目錄

目錄

譯者序

原書前言

致謝

作者簡介

第1章引言1

11摩爾定律1

12工藝發展的影響:05 μ m~28nm的電源管理晶片1

121MOSFET結構1

122電晶體的尺度效應6

123漏電流功耗8

13先進工藝產品中電源管理集成電路的挑戰12

131多閾值電壓工藝12

132性能優化13

133與版圖有關的鄰近效應16

134對電路設計的影響17

14電源管理模塊中的基本定義18

141負載調整率18

142瞬態電壓變化19

143傳輸損耗和開關損耗20

144功率轉換效率21

參考文獻21

第2章低壓差線性(LDO)穩壓器設計23

21LDO穩壓器的基本結構24

211傳輸器件的類型26

22補償科技28

221極點分佈29

222零點分佈和右半平面零點34

23LDO穩壓器設計考慮36

231電壓差36

232效率38

233線性/負載調整率39

234負載電流突變引起的瞬態輸出電壓變化40

24類比LDO穩壓器43

241主極點補償的特性43

242無電容結構特點48

243低電壓無電容LDO穩壓器的設計54

244在多級無電容LDO穩壓器中通過使用電流迴響補償减少最小負載電流限制57

245具有前饋通路和動態增益調整的多級LDO穩壓器65

25LDO穩壓器的設計指導70

251模擬提示和結果分析71

252在交流分析模擬中打破閉環的方法72

253具有主極點補償的LDO穩壓器的模擬實例74

26數位LDO穩壓器設計82

261基本數位LDO穩壓器83

262具有網格非同步自定時控制(LASC)科技的數位LDO穩壓器85

263動態電壓縮減(DVS)88

27具有類比動態電壓縮減(ADVS)科技的開關數位/類比低壓差線性(D/A-LDO)

穩壓器98

271ADVS科技98

272可切換的D/A-LDO穩壓器101

參考文獻107

第3章開關電源穩壓器的設計109

31基本概念109

32控制方法與工作原理概述112

33開關穩壓器的小訊號模型與補償方法117

331電壓模式開關穩壓器的小訊號建模117

332閉環電壓模式中開關穩壓器的小訊號建模121

333電流模式開關穩壓器的小訊號建模136

參考文獻153

第4章基於紋波的控制科技(第1部分)154

41基於紋波控制的基本拓撲結構154

411遲滯控制157

412導通時間控制159

413關斷時間控制163

414具有峰值電壓控制和波谷電壓控制的恒定頻率科技165

415基於紋波控制拓撲結構總結166

42導通時間控制型降壓轉換器的穩定標準168

421穩定性判據的推導168

422輸出電容的選擇179

43採用小阻值RESR的多層陶瓷電容設計科技182

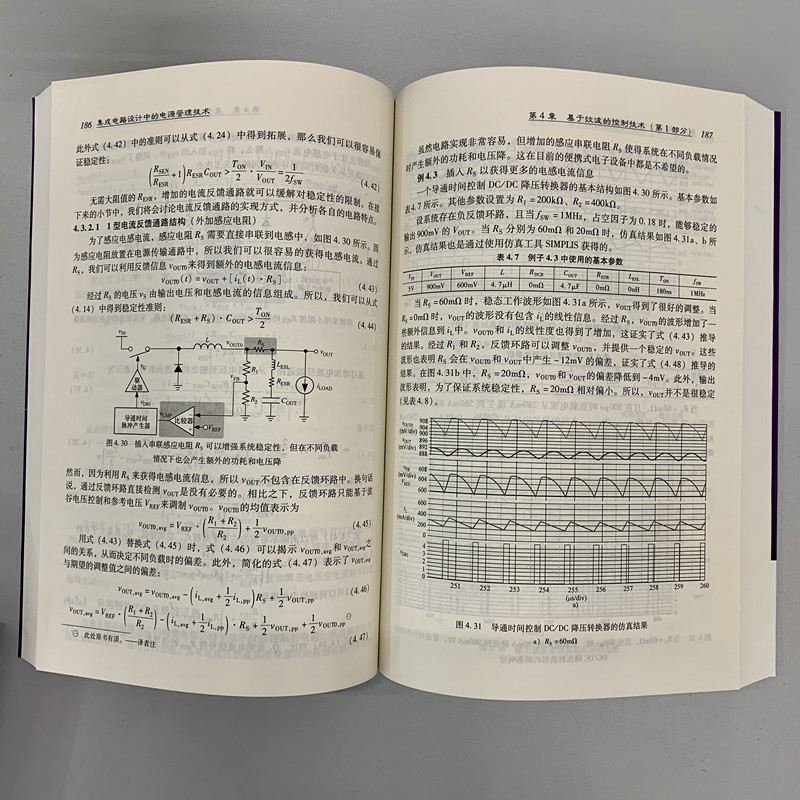

431採用附加斜坡訊號183

432採用額外的電流迴響通路184

433具有附加電流迴響通路的導通時間控制模式的比較232

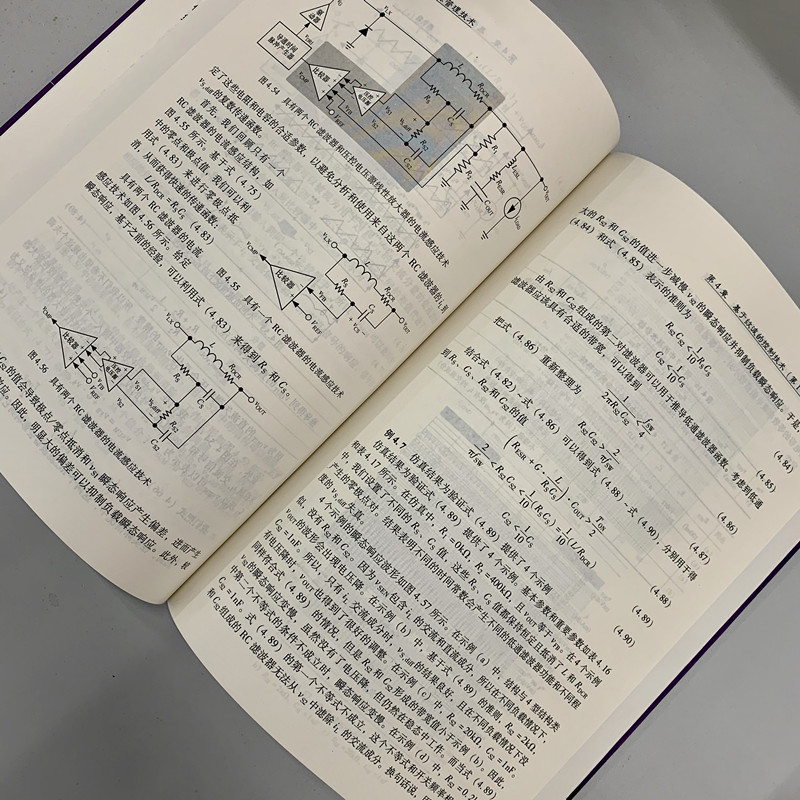

434採用紋波整形科技補償小阻值RESR234

435紋波整形功能的實驗結果239

參考文獻246

第5章基於紋波的控制科技(第2部分)247

51增强電壓調整效能的設計科技247

511直流電壓調整精度247

512用於紋波控制的電壓二次方結構247

513採用附加斜坡或者電流迴響通路的電壓二次方實时控制科技251

514採用小阻值RESR的電壓二次方結構中的比較器253

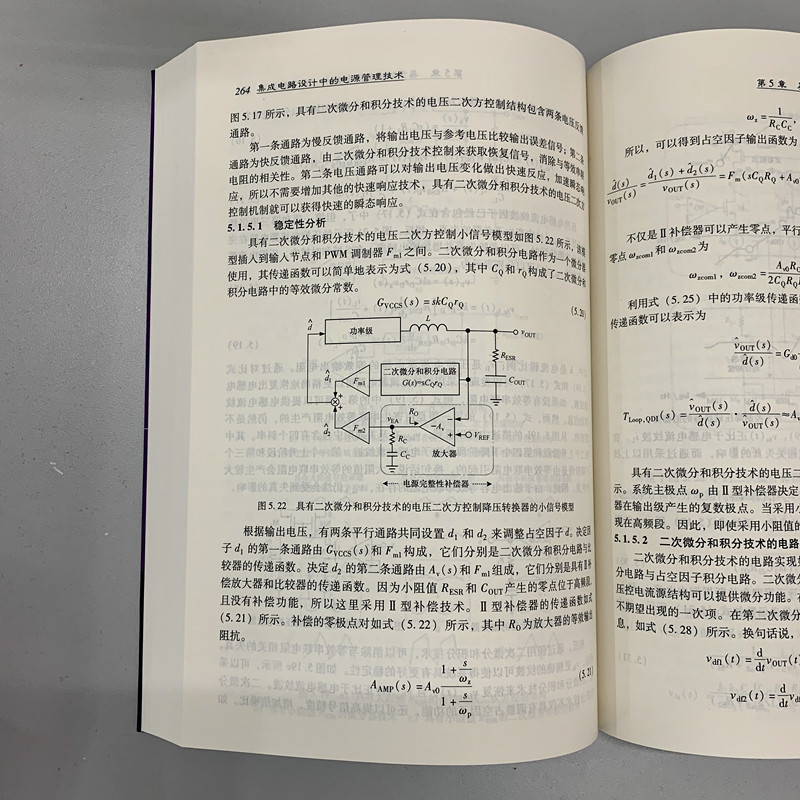

515採用小阻值RESR的具有二次微分和積分科技的基於紋波控制科技261

516魯棒性强的紋波調整器269

52對於開關頻率變化降低電磁干擾的分析271

521迴響訊號抗干擾能力的提高273

522旁路通路對迴響訊號高頻雜訊的濾波273

523鎖相環調製器科技275

524不同vIN、vOUT、iLOAD情况下頻率變化的分析276

525用於偽恒定fSW的自我調整導通時間控制器286

53用於偽恒定fSW的最優化導通時間控制器293

531導通時間控制的優化算灋294

532具有等效vIN和vOUT,eq的Ⅰ型最優化導通時間控制器294

533具有等效vDUTY的Ⅱ型最優化導通時間控制器302

534頻率鉗比特器304

535不同導通時間控制器的比較304

536最優化導通時間控制器的模擬結果305

537最優化導通時間控制器的實驗結果309

參考文獻313

第6章單電感多輸出轉換器315

61單電感多輸出轉換器的基本拓撲結構315

611結構316

612交叉調整316

62單電感多輸出轉換器的應用317

621片上系統317

622可擕式電子系統318

63單電感多輸出轉換器的設計指導319

631能量傳輸通路319

632控制方法分類327

633設計目標329

64用於片上系統的單電感多輸出轉換器331

641電感電流控制中的疊加定理331

642雙模能量傳輸方法333

643能量模式轉換334

644自動能量旁路337

645瞬態交叉調整的消除338

646電路實現342

647實驗結果351

65平板電腦應用中的單電感多輸出轉換器科技361

651單電感多輸出轉換器中的輸出獨立柵極驅動控制361

652單電感多輸出轉換器中的連續導通模式/綠色模式相對忽略能量控制369

653單電感多輸出轉換器中的雙向動態斜率補償378

654電路實現383

655實驗結果390

參考文獻404

第7章基於開關的電池充電器406

71引言406

711純充電狀態409

712直接供電狀態409

713斷開狀態410

714充電和供電狀態410

72基於開關的電池充電器的小訊號分析411

73閉環等效模型416

74採用PSIM進行模擬423

75渦輪加速升壓充電器428

76內寘電阻對充電器系統的影響432

77設計實例:連續內建電阻監測436

771連續內建電阻監測的操作436

772連續內建電阻監測的電路實現438

773實驗結果442

參考文獻444

第8章能量收集系統445

81能量收集系統概述445

82能量收集源447

821振動電磁換能器449

822壓電發電機451

823靜電能量發生器451

824風力發電裝置453

825熱電式發電機454

826太陽電池456

827磁線圈457

828射頻/無線460

83能量收集電路461

831能量收集電路的基本概念461

832交流電源能量收集電路464

833直流電源能量收集電路469

84最大功率點跟踪471

841最大功率點跟踪的基本概念471

842阻抗匹配471

843電阻類比473

844最大功率點跟踪方法474

參考文獻479

高雄鍾**[0966***434] 7分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 桃園柳**[0920***977] 12分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 基隆謝**[0946***572] 25分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 桃園王**[0978***180] 4分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 臺北謝**[0986***536] 25分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 臺南錢**[0938***175] 20分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 臺北楊**[0918***885] 15分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 新竹黃**[0918***538] 12分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 嘉義陳**[0978***781] 半小時前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 桃園陳**[0956***780] 5分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 桃園鍾**[0938***900] 11分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 高雄錢**[0938***438] 7分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 嘉義王**[0938***351] 25分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 基隆鍾**[0920***421] 12分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 嘉義周**[0933***571] 12分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 臺中吳**[0946***366] 4分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 臺中鄭**[0966***618] 4分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 高雄趙**[0986***275] 15分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 臺中陳**[0978***775] 25分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 嘉義鄭**[0918***297] 20分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 臺北劉**[0960***436] 11分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 臺中方**[0938***158] 25分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 基隆黃**[0998***945] 20分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 高雄吳**[0933***674] 2分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 嘉義柳**[0986***635] 25分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 桃園鄭**[0966***518] 2分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 桃園趙**[0918***670] 5分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 新竹陳**[0938***633] 4分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 臺南符**[0956***205] 25分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 臺北朱**[0966***972] 15分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 新北符**[0956***451] 15分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 新竹符**[0920***786] 4分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 桃園黃**[0938***925] 7分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 基隆孫**[0978***362] 12分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 嘉義謝**[0986***557] 5分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 新北仲**[0960***238] 2分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 臺中方**[0986***746] 7分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 臺南李**[0932***424] 11分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 臺中朱**[0978***924] 11分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 臺北謝**[0918***646] 7分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 臺中王**[0932***386] 4分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 高雄鍾**[0946***249] 4分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 新竹吳**[0920***518] 15分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 基隆仲**[0998***602] 5分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 臺中鍾**[0918***147] 4分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 新北楊**[0932***420] 12分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 新北黃**[0998***213] 20分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 新竹黃**[0938***868] 25分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 高雄符**[0998***424] 15分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300) 臺南孫**[0932***931] 15分鐘前【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】 - 【三維晶片集成與封裝技術】+【積體電路設計中的電源管理科技】(兩册,價:2300)