【功率半導體器件封裝技術】

內容簡介

本書主要闡述了功率半導體器件封裝技術的發展歷程及其涉及的資料、工藝、品質控制和產品認證等方面的基本原理和方法。 同時對功率半導體器件的電性能測試、失效分析、產品設計、模擬應力分析和功率模組的封裝技術做了較為系統的分析和闡述,也對第三代寬禁帶功率半導體器件的封裝技術及應用於特殊場景(如汽車和航太領域)的功率器件封裝技術及質量要求進行了綜述。 通過對本書的學習,讀者能够瞭解和掌握功率半導體器件的封裝技術和質量要求,由此展開並理解各種封裝技術的目的、特點和應用場合,從而深刻理解功率半導體器件的封裝實現過程及其重要性。

本書可作為各大專院校微電子、集成電路及電晶體封裝專業開設封裝課程的規劃教材和教輔用書,也可供工程技術人員及電晶體封裝從業人員參攷。

作者簡介

本書作者團隊由長期工作在電晶體封測行業及科研研究機構的專業人士組成,主要成員及簡介如下:

朱正宇,通富微電子股份有限公司總監,6 sigma黑帶大師。 曾在世界著名電晶體公司(三星、仙童、霍尼韋爾公司)任職科技經理等職。。 熟悉精通電晶體封裝,在內互聯、IGBT、太陽能、射頻及SiC模塊等領域發表多項國內外專利和文章,長期負責功率器件及汽車電晶體業務的研發管理、質量改善和精益生產。 曾獲2018年南通市紫琅英才,2019年江海人才。

王可,中國科學院微電子所高級工程師,長期從事資料、封裝及可靠性相關的工程和研究工作。 主持和參與國家及省部級項目十餘項,發表期刊和會議文章二十餘篇、專利二十餘項。 作為行業權威標準製定顧問,參與行業多項權威標準製定。

蔡志匡,南京郵電大學教授、博士生導師,南京郵電大學產學研合作處副處長、集成電路科學與工程學院執行副院長。 入選江蘇省333高層次人才培養工程、江蘇省六大人才高峰、江蘇省青年科技人才托舉工程。 研究方向是集成電路測試,主持國家重點研發計畫等項目二十多項,發表論文四十餘篇,申請專利五十多項。

肖廣源,投資創建無錫華友微電子有限公司和上海華友金裕微電子有限公司。 主要從事集成電路行業晶圓、框架以及封裝後的表面處理關鍵制程,處於細分行業領先地位,並獲得相關專利27項。

目錄

序

前言

致謝

第章功率電晶體封裝的定義和分類1

1.1電晶體的封裝1

1.2功率半導體器件的定義3

1.3功率電晶體發展簡史4

1.4半導體材料的發展6

參考文獻8

第章功率半導體器件的封裝特點9

2.1分立器件的封裝9

2.2功率模組的封裝12

2.2.1功率模組封裝結構12

2.2.2智慧功率模組14

2.2.3功率電子模塊15

2.2.4大功率灌膠類別模組16

2.2.5雙面散熱功率模組16

2.2.6功率模組封裝相關科技16

參考文獻19

第章典型的功率封裝過程20

3.1基本流程20

3.2劃片20

3.2.1貼膜21

3.2.2膠膜選擇22

3.2.3特殊的膠膜23

3.2.4矽的資料特性25

3.2.5晶圓切割26

3.2.6劃片的工藝27

3.2.7晶圓劃片工藝的重要質量缺陷29

3.2.8雷射劃片30

3.2.9超聲波切割32

3.3裝片33

3.3.1膠聯裝片34

3.3.2裝片常見問題分析37

3.3.3焊料裝片41

3.3.3.1焊料裝片的過程和原理41

3.3.3.2焊絲焊料的裝片過程46

3.3.3.3溫度曲線的設定48

3.3.4共晶焊接49

3.3.5銀燒結54

3.4內互聯鍵合59

3.4.1超聲波壓焊原理60

3.4.2金/銅線鍵合61

3.4.3金/銅線鍵合的常見失效機理72

3.4.4鋁線鍵合之超聲波冷壓焊73

3.4.4.1焊接參數響應分析74

3.4.4.2焊接材料品質分析76

3.4.5不同資料之間的焊接冶金特性綜述82

3.4.6內互聯焊接質量的控制85

3.5塑封90

3.6電鍍93

3.7打標和切筋成形97

參考文獻99

第章功率器件的測試和常見不良分析100

4.1功率器件的電特性測試100

4.1.1MOSFET產品的靜態參數測試100

4.1.2動態參數測試103

4.1.2.1擊穿特性103

4.1.2.2熱阻103

4.1.2.3栅電荷測試105

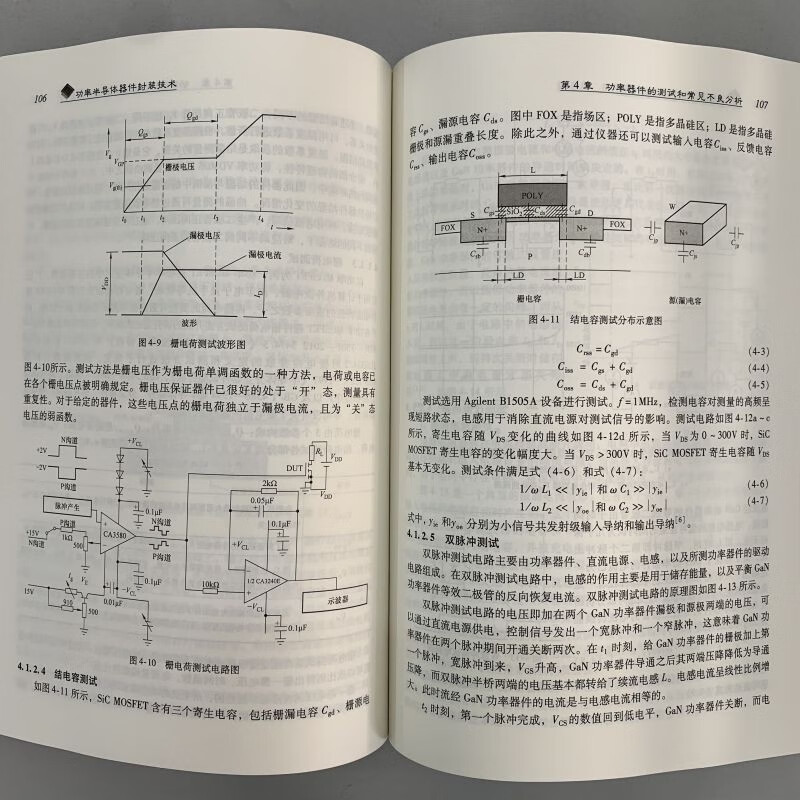

4.1.2.4結電容測試106

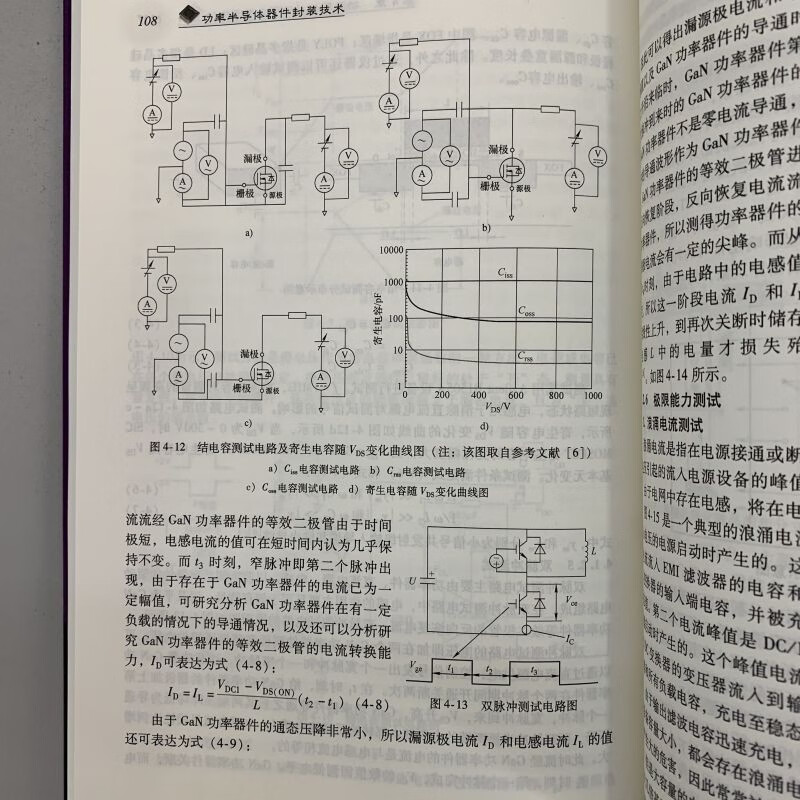

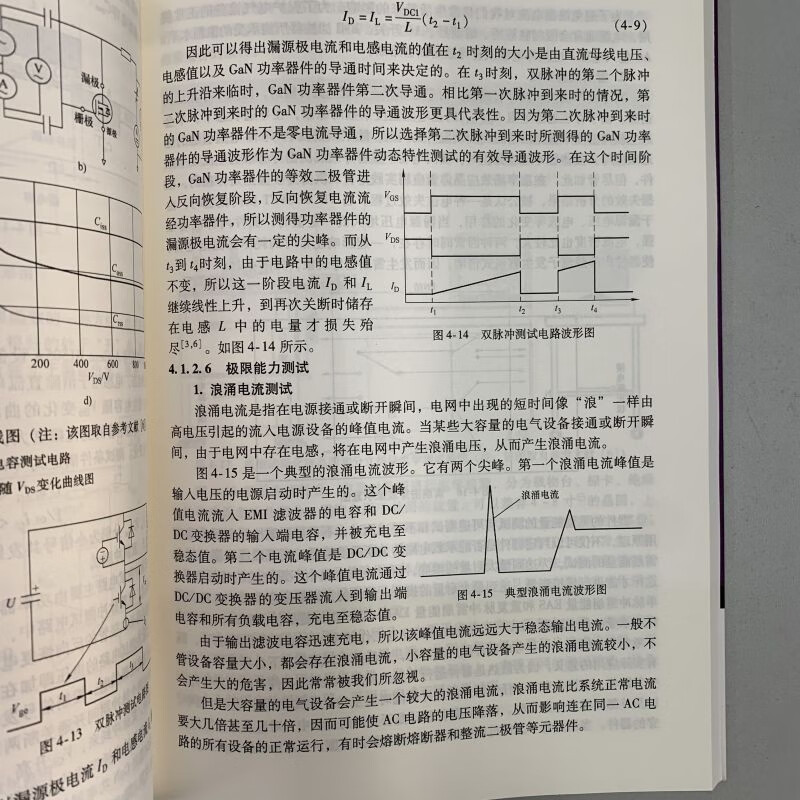

4.1.2.5雙脈衝測試107

4.1.2.6極限能力測試109

4.2晶圓(CP)測試111

4.3封裝成品測試(FT)113

4.4系統級測試(SLT)115

4.5功率器件的失效分析116

4.5.1封裝缺陷與失效的研究方法論117

4.5.2引發失效的負載類型118

4.5.3封裝過程缺陷的分類118

4.5.4封裝體失效的分類123

4.5.5加速失效的因素125

4.6可靠性測試125

參考文獻129

第章功率器件的封裝設計131

5.1資料和結構設計131

5.1.1引脚寬度設計131

5.1.2框架引脚整形設計132

5.1.3框架內部設計132

5.1.4框架外部設計135

5.1.5封裝體設計137

5.2封裝工藝設計139

5.2.1封裝內互聯工藝設計原則139

5.2.2裝片工藝設計一般規則140

5.2.3鍵合工藝設計一般規則141

5.2.4塑封工藝設計145

5.2.5切筋打彎工藝設計146

5.3封裝的散熱設計146

參考文獻150

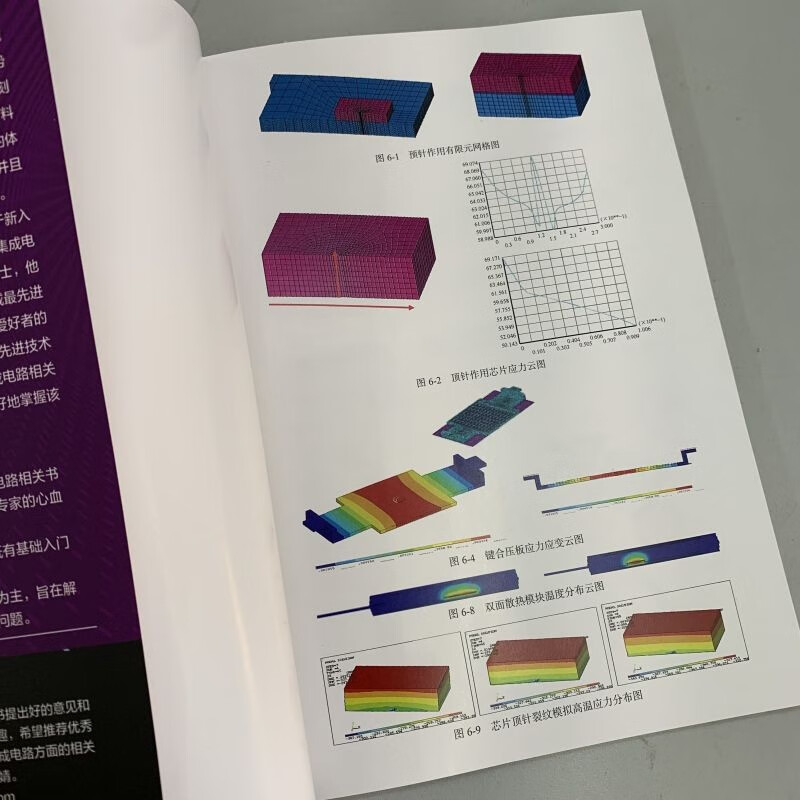

第章功率封裝的模擬技術151

6.1模擬的基本原理151

6.2功率封裝的應力模擬152

6.3功率封裝的熱模擬156

6.4功率封裝的可靠性加載模擬157

參考文獻161

第章功率模組的封裝162

7.1功率模組的工藝特點及其發展162

7.2典型的功率模組封裝工藝164

7.3模塊封裝的關鍵工藝170

7.3.1銀燒結171

7.3.2粗銅線鍵合172

7.3.3植PIN174

7.3.4端子焊接176

第章車規級半導體器件封裝特點及要求178

8.1IATF 16949:2016及汽車生產體系工具179

8.2汽車電晶體封裝生產的特點186

8.3汽車電晶體產品的品質認證187

8.4汽車功率模組的品質認證191

8.5ISO 26262介紹193

參考文獻194

第章第三代寬禁帶功率電晶體封裝195

9.1第三代寬禁帶電晶體的定義及介紹195

9.2SiC的特質及晶圓製備196

9.3GaN的特質及晶圓製備198

9.4第三代寬禁帶功率半導體器件的封裝200

9.5第三代寬禁帶功率半導體器件的應用201

第章特種封裝/宇航級封裝204

10.1特種封裝概述204

10.2特種封裝工藝206

10.3特種封裝常見的封裝失效210

10.4特種封裝可靠性問題213

10.5特種封裝未來發展217

參考文獻221

附錄電晶體術語中英文對照222

書摘插畫

--------------------------------------------------------------------------------

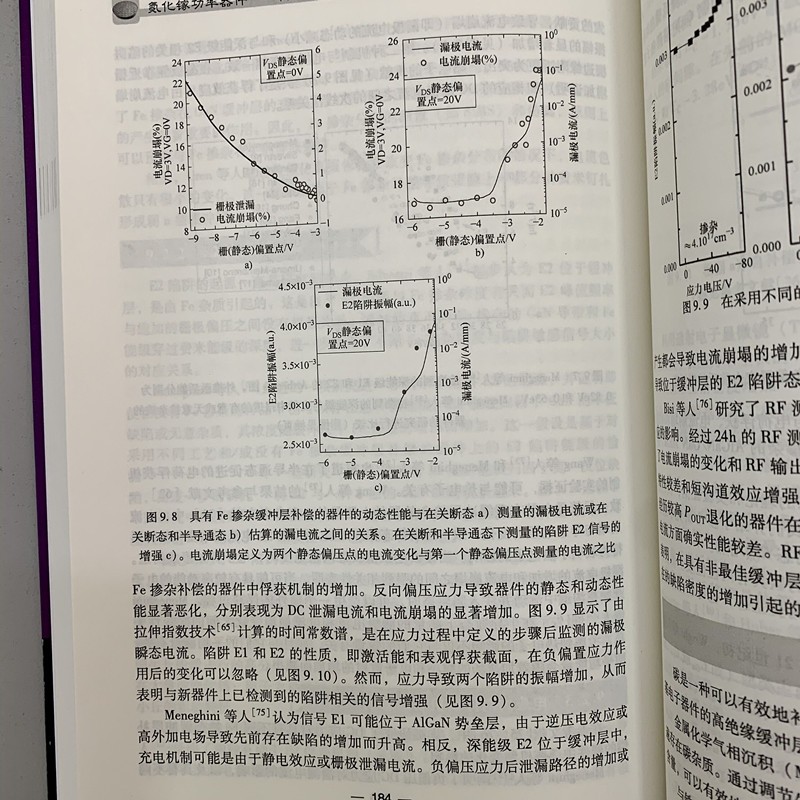

【氮化鎵功率器件資料、應用及可靠性】

內容簡介

本書重點討論了與氮化鎵(GaN)器件相關的內容,共分15章,每一章都圍繞不同的主題進行論述,涵蓋GaN資料、與CMOS工藝相容的GaN工藝、不同的GaN器件設計、GaN器件的建模、GaN器件的可靠性表徵以及GaN器件的應用。 本書的特點是每一章都由全球不同的從事GaN研究機構的專家撰寫,引用了大量的代表新成果的文獻,適合於從事GaN科技研究的科研人員、企業研發人員,以及工程師閱讀,也可作為微電子及相關專業的高年級大學生、研究生和教師的參攷用書。

目錄

原書前言

第1章GaN的特性及優點1

1.1總體背景1

1.2GaN資料2

1.3極化效應5

1.4GaN基FET8

1.5天然超級結(NSJ)結構10

1.6導通電阻和擊穿電壓13

1.7低壓器件14

1.8高壓器件18

1.9GaN垂直功率器件的未來研究21

參考文獻22

第2章襯底和資料24

2.1襯底概述25

2.2金屬有機化學氣相沉積26

2.2.1半絕緣(S.I.)的(Al,Ga)N層的製造28

2.2.2n型和p型摻雜29

2.2.3AlGaN/GaN異質結構30

2.3陷阱和色散31

2.4橫向功率開關器件外延結構的製備31

2.4.1矽襯底上電流阻斷層的沉積32

2.4.2碳化矽襯底上電流阻斷層的沉積33

2.4.3藍寶石襯底上電流阻斷層的沉積33

2.4.4栅控層生長35

2.5垂直器件35

2.6展望39

2.6.1InAlN和AlInGaN墊座層39

2.6.2基於非c面GaN的器件40

參考文獻41

第3章Si上GaN CMOS相容工藝47

3.1Si上GaN外延47

3.2Si上GaN無Au工藝49

3.3無Au歐姆接觸54

3.3.1AlGaN勢壘層凹槽55

3.3.2歐姆合金優化55

3.3.3Ti/Al比56

3.3.4歐姆金屬堆疊底部的Si層57

3.4Ga污染問題58

3.5結論61

參考文獻61

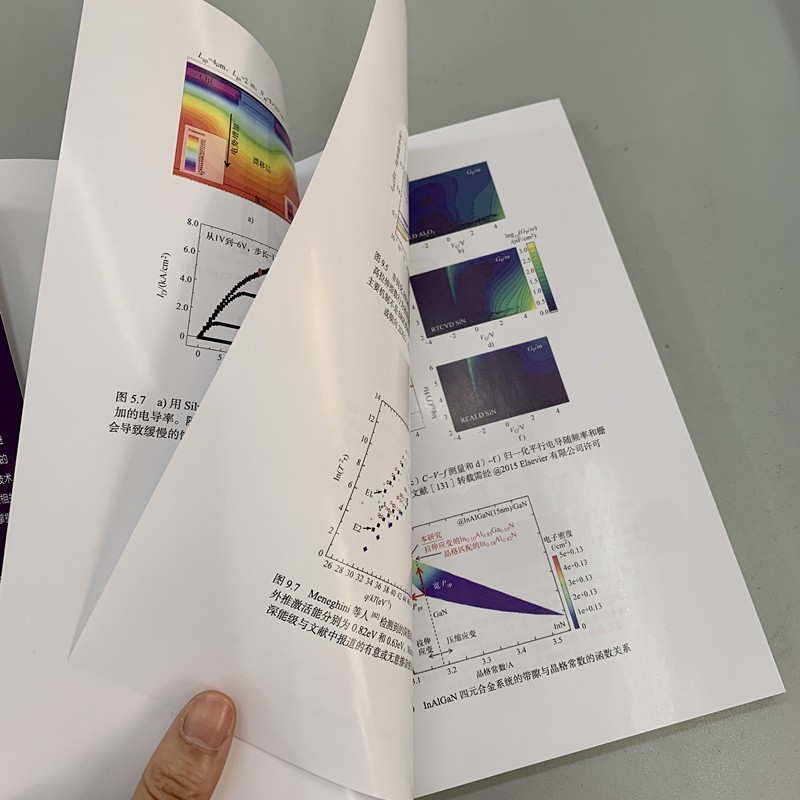

第4章橫向GaN器件的功率應用(從kHz到GHz)62

4.1簡介62

4.2AlGaN/GaN HEMT的歷史62

4.3色散的處理64

4.4用於毫米波的GaN66

4.5N極性GaN發展的歷史回顧69

4.6電力電子中GaN的應用77

4.7結論83

參考文獻83

第5章垂直GaN科技——資料、器件和應用91

5.1引言91

5.2器件拓撲93

5.2.1垂直器件與橫向器件的比較93

5.3CAVET的演變95

5.4CAVET設計97

5.4.1器件成功運行所需的關鍵部分的討論97

5.5CAVET的關鍵組成部分99

5.5.1電流阻斷層103

5.5.2效能和成本105

5.6體GaN襯底的作用106

5.7RF應用的CAVET107

5.8結論107

參考文獻108

第6章GaN基納米線電晶體110

6.1簡介110

6.1.1自下而上的納米線器件:GaN納米線場效應電晶體111

6.1.2自上而下的納米線器件113

6.2三栅GaN功率MISFET114

6.2.1三栅GaN功率電晶體的其他考慮116

6.3用於RF應用的納米線:新增gm的線性度120

6.4納米結構的GaN肖特基勢壘二極體122

6.4.1GaN SBD的納米結構陽極123

6.5結論126

參考文獻127

第7章深能級表徵:電學和光學方法130

7.1簡介130

7.2DLTS和DLOS基礎131

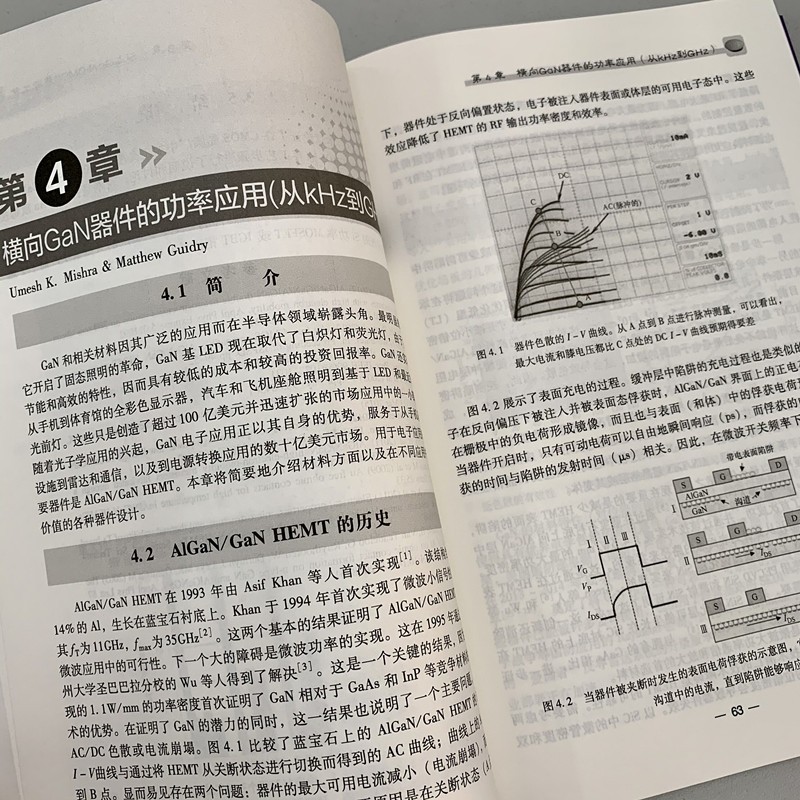

7.2.1C-DLTS132

7.2.2C-DLOS133

7.2.3C-DLTS和C-DLOS對HEMT的適用性134

7.2.4I-DLTS和I-DLOS135

7.3DLTS和DLOS在GaN HEMT中的應用137

7.3.1利用填充脈衝對陷阱進行空間定位137

7.3.2利用量測偏差對陷阱進行空間定位140

7.3.3量測空間局限性的陷阱的其他方法142

7.4結論143

參考文獻144

第8章GaN HEMT的建模:從器件級模擬到虛擬原型146

8.1簡介146

8.2器件級模擬148

8.2.1脈衝模式行為149

8.3非優化的緩衝科技150

8.4優化的緩衝層工藝154

8.4.1AC電容155

8.4.2關斷態擊穿157

8.5Spice模型開發和校準159

8.6應用板的特性和模擬161

8.6.1正常關斷pGaN電晶體163

8.6.2正常開啟HEMT:共源共栅設計165

8.7結論170

參考文獻171

第9章GaN基HEMT中限制效能的陷阱:從固有缺陷到常見雜質173

9.1表面相關的俘獲177

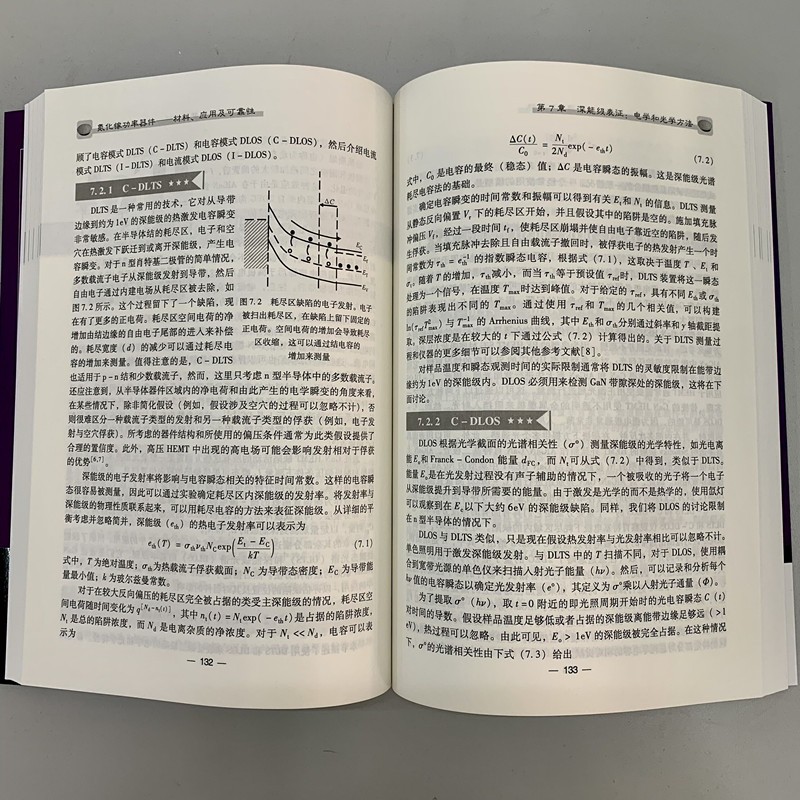

9.2Fe摻雜的影響179

9.2.1深能級E2的特性及Fe摻雜的影響180

9.2.2E2陷阱的起源182

9.2.3電應力對俘獲機制的影響183

9.3C摻雜的影響185

9.4金屬絕緣體電晶體高電子遷移率電晶體(MIS-HEMT)的俘獲機制193

9.4.1正柵極偏壓引起的俘獲193

9.4.2快俘獲和慢俘獲機理分析195

9.4.3提高俘獲效應的資料和沉積科技196

參考文獻199

第10章矽上共源共栅GaNHEMT:結構、效能、製造和可靠性209

10.1共源共栅GaN HEMT的動機和結構209

10.2共源共栅GaN HEMT的功能和優點210

10.3共源共栅GaN HEMT的關鍵應用和效能優勢211

10.3.1無二極體半橋結構211

10.3.2柵極驅動的考慮212

10.4市場上的產品213

10.5應用和主要性能優勢214

10.5.1圖騰柱功率因數校正(PFC)電路214

10.5.2PV逆變器215

10.5.3帶GaN AC-DC PFC和全橋諧振開關LLC DC-DC變換器的一體式電源216

10.6共源共栅GaN HEMT的認證和可靠性217

10.6.1JEDEC認證218

10.6.2擴展的認證/可靠性測試218

10.6.3工作和本征壽命測試219

10.7卓越製造221

10.8單片上的E模式GaN222

10.9未來展望223

10.9.1下一代產品223

10.9.2知識產權考慮223

10.9.3小結223

參考文獻224

第11章栅注入電晶體:E模式工作和電導率調製225

11.1GIT的工作原理225

11.2GIT的DC和開關效能228

11.3關於GIT可靠性的最新研究231

11.4GIT在實際開關系統中的應用234

11.5面向未來電力電子的先進GIT科技237

11.6結論240

參考文獻240

第12章氟注入E模式電晶體242

12.1簡介:III-氮化物異質結構中的氟:Vth魯棒性控制242

12.2氟注入的物理機制243

12.2.1F电浆離子注入的原子模型243

12.2.2AlGaN/GaN異質結構中F離子的穩定性245

12.2.3F離子周圍的電子結合能247

12.3F離子注入E模式GaNMIS—HEMT249

12.3.1GaN MIS—HEMT249

12.3.2帶有部分凹槽的F離子注入勢壘層的GaNMIS—HEMT252

12.3.3GaN智慧功率晶片255

12.4結論259

參考文獻260

第13章GaN高壓功率電晶體的漂移效應262

13.1簡介262

13.2漂移效應及其物理機制262

13.2.1概述262

13.2.2基本物理理解263

13.2.3對器件工作條件的依賴性265

13.3GaN功率開關電晶體中的漂移現象266

13.3.1導通態下的動態電阻(Ron_dyn)266

13.3.2閾值電壓偏移273

13.3.3Kink效應275

13.4科技對策276

13.4.1優化的外延緩衝層設計276

13.4.2减小關鍵器件區域的電場277

參考文獻279

第14章額定電壓650V的GaN功率器件的可靠性問題283

14.1簡介283

14.2無Au歐姆接觸的可靠性283

14.2.1歐姆接觸可靠性簡介283

14.2.2無Au歐姆接觸件的加工284

14.2.3應力和量測順序284

14.2.4無Au歐姆接觸的可靠性評估286

14.2.5結論290

14.3MIS—HEMT柵極介質的可靠性292

14.3.1簡介292

14.3.2實驗292

14.3.3正向偏置條件下對洩漏電流的分析294

14.3.4反向偏壓條件下對洩漏電流的分析295

14.3.5體SiN缺陷態分析297

14.3.6TDDB研究298

14.3.7結論299

14.4緩衝層堆疊可靠性——關斷態高壓漏極應力300

14.4.1簡介300

14.4.2電流傳導機制301

14.4.3高溫反向偏置302

14.4.4高壓關斷態漏極應力303

14.4.5結論303

參考文獻304

第15章GaN電晶體的開關特性:系統級問題307

15.1E模式和共源共栅GaN的開關特性307

15.1.1開關損耗機制307

15.1.2封裝影響309

15.1.3硬開關與軟開關的比較312

15.2共源共栅GaN的特殊問題313

15.2.1封裝對柵極擊穿的影響313

15.2.2電容失配的影響314

15.3GaN器件的柵極驅動器設計319

15.3.1di/dt問題319

15.3.2dv/dt問題320

15.4系統級影響322

15.4.13D集成的負載點變換器322

15.4.2隔離的DC—DC變換器324

15.4.3MHz級圖騰柱PFC整流器327

15.4.4高密度插牆式轉接器328

15.5結論331

參考文獻331

書摘插畫

--------------------------------------------------------------------------------

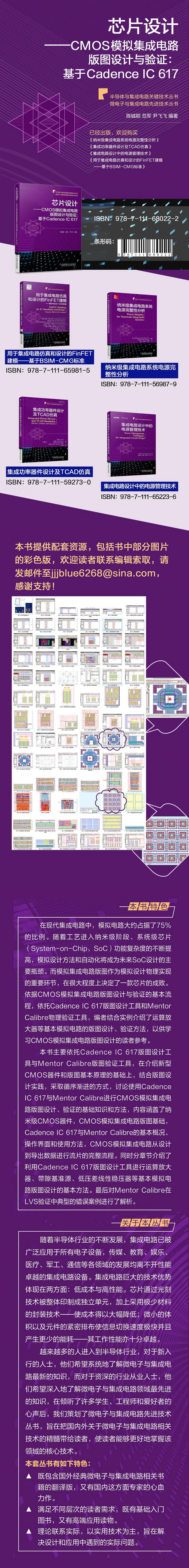

【晶片設計CMOS類比集成電路版圖設計與驗證】

內容簡介

本書主要依託Cadence IC 617版圖設計工具與Mentor Calibre版圖驗證工具,在介紹新型CMOS器件和版圖基本原理的基礎上,結合版圖設計實踐,採取循序漸進的管道,討論使用Cadence IC 617與Mentor Calibre進行CMOS類比集成電路版圖設計、驗證的基礎知識和方法,內容涵蓋了納米級CMOS器件,CMOS類比集成電路版圖基礎, Cadence IC 617與Mentor Calibre的基本概況、操作介面和使用方法,CMOS類比集成電路從設計到匯出數據進行流片的完整流程。 同時分章節介紹了利用Cadence IC 617版圖設計工具進行運算放大器、帶隙基準源、低壓差線性穩壓器等基本類比電路版圖設計的基本方法。* 後對Mentor Calibre在LVS驗證中典型的錯誤案例進行了解析。

本書通過結合器件知識、電路理論和版圖設計實踐,使讀者深刻瞭解CMOS電路版圖設計和驗證的規則、流程和基本方法,對於進行CMOS類比集成電路學習的在校高年級大學生、碩士生和博士生,以及從事集成電路版圖設計與驗證的工程師,都會起到有益的幫助。

目錄

前言

第1章納米級CMOS器件1

1.1概述1

1.2平面全耗盡絕緣襯底上矽(FD-SOI)MOSFET4

1.2.1採用薄氧化埋層的原因5

1.2.2超薄體中的二維效應8

1.3FinFET11

1.3.1三栅以及雙栅FinFET12

1.3.2實際中的結構選擇19

1.4基於gm/ID的設計方法20

1.4.1類比集成電路的層次化設計20

1.4.2gm/ID設計方法所處的地位21

1.4.3gm/ID設計方法的優勢22

1.4.4基於Vov的設計方法23

1.4.5gm/ID設計方法詳述27

1.4.6基於gm/ID的設計實例31

第2章CMOS類比集成電路版圖基礎33

2.1CMOS類比積體電路設計流程33

2.2CMOS類比集成電路版圖定義36

2.3CMOS類比集成電路版圖設計流程37

2.3.1版圖規劃38

2.3.2版圖設計實現39

2.3.3版圖驗證40

2.3.4版圖完成41

2.4版圖設計通用規則42

2.5版圖佈局44

2.5.1對稱約束下的電晶體級佈局45

2.5.2版圖約束下的層次化佈局46

2.6版圖佈線50

2.7CMOS類比集成電路版圖匹配設計54

2.7.1CMOS工藝失配機理54

2.7.2元器件版圖匹配設計規則56

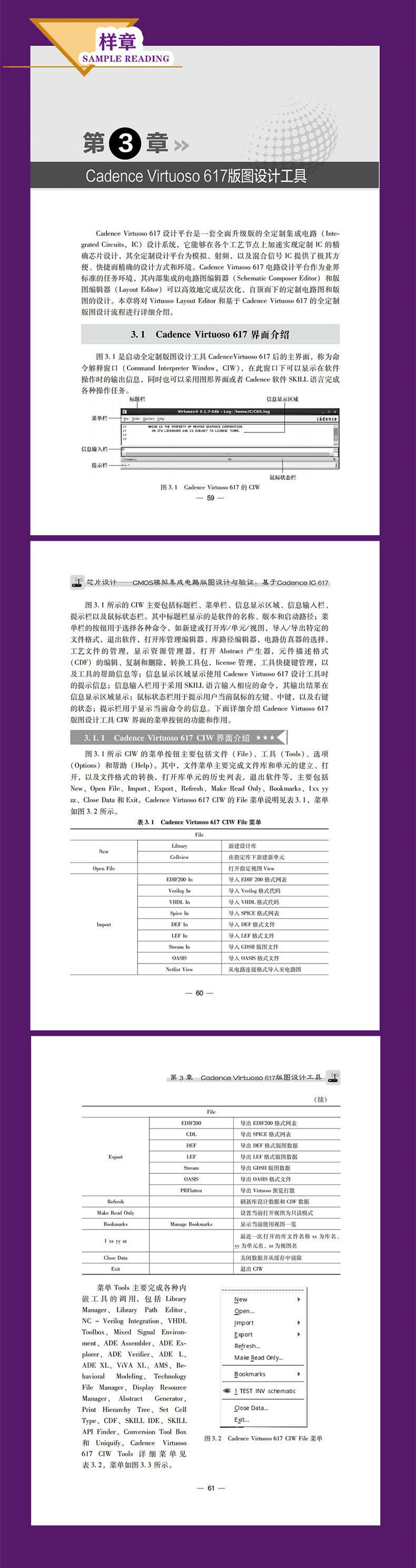

第3章Cadence Virtuoso 617版圖設計工具59

3.1Cadence Virtuoso 617介面介紹59

3.1.1Cadence Virtuoso 617 CIW介面介紹60

3.1.2Cadence Virtuoso 617 Library Manager介面介紹66

3.1.3Cadence Virtuoso 617 Library Path Editor操作介紹85

3.1.4Cadence Virtuoso 617 Layout Editor介面介紹96

3.2Virtuoso基本操作124

3.2.1創建圓形124

3.2.2創建矩形125

3.2.3創建路徑126

3.2.4創建標識名127

3.2.5調用器件和陣列128

3.2.6創建接觸孔和通孔130

3.2.7創建環形圖形131

3.2.8移動命令132

3.2.9複製命令133

3.2.10拉伸命令134

3.2.11删除命令135

3.2.12合併命令135

3.2.13改變層次關係命令136

3.2.14切割命令138

3.2.15旋轉命令139

3.2.16内容命令140

3.2.17分離命令141

3.2.18改變形狀命令142

3.2.19版圖層擴縮命令143

第4章Mentor Calibre版圖驗證工具145

4.1Mentor Calibre版圖驗證工具簡介145

4.2Mentor Calibre版圖驗證工具調用145

4.2.1採用Virtuoso Layout Editor內嵌管道啟動146

4.2.2採用Calibre圖形介面啟動147

4.2.3採用Calibre View檢視器啟動149

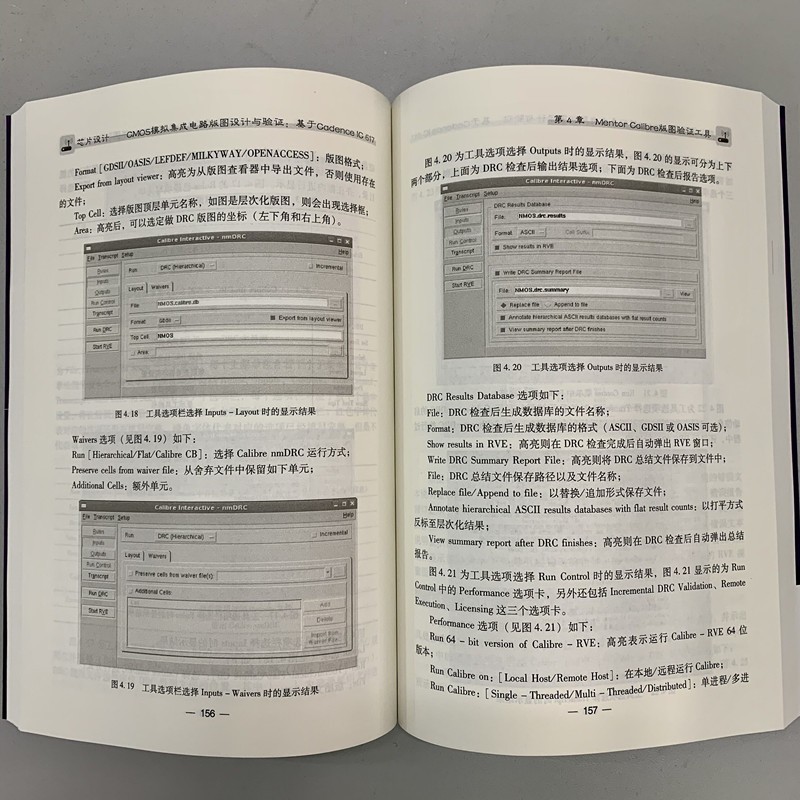

4.3Mentor Calibre DRC驗證151

4.3.1Calibre DRC驗證簡介151

4.3.2Calibre nmDRC介面介紹153

4.3.3Calibre nmDRC驗證流程舉例159

4.4Mentor Calibre nmLVS驗證170

4.4.1Calibre nmLVS驗證簡介170

4.4.2Calibre nmLVS介面介紹170

4.4.3Calibre LVS驗證流程舉例183

4.5Mentor Calibre寄生參數選取(PEX)194

4.5.1Calibre PEX驗證簡介194

4.5.2Calibre PEX介面介紹194

4.5.3Calibre PEX流程舉例204

第5章CMOS類比集成電路版圖設計與驗證流程213

5.1設計環境準備213

5.2單級跨導放大器電路的建立和前模擬219

5.3跨導放大器版圖設計230

5.4跨導放大器版圖驗證與參數選取241

5.5跨導放大器電路後模擬258

5.6輸入輸出單元環設計264

5.7主體電路版圖與輸入輸出單元環的連接272

5.8匯出GDSII檔案277

第6章運算放大器的版圖

設計280

6.1運算放大器基礎280

6.2運算放大器的基本特性和分類281

6.2.1運算放大器的基本特性281

6.2.2運算放大器的性能參數282

6.2.3運算放大器的分類286

6.3單級折疊共源共栅運算放大器的版圖設計291

6.4兩級全差分密勒補償運算放大器的版圖設計296

6.5電容—電壓轉換電路版圖設計300

第7章帶隙基準源與低壓差線性穩壓器的版圖設計308

7.1帶隙基準源的版圖設計308

7.1.1帶隙基準源基本原理308

7.1.2帶隙基準源版圖設計實例314

7.2低壓差線性穩壓器的版圖設計318

7.2.1低壓差線性穩壓器的基本原理319

7.2.2低壓差線性穩壓器版圖設計實例321

第8章Calibre LVS常見錯誤解析326

8.1LVS錯誤對話方塊(RVE對話方塊)326

8.2誤連接334

8.3短路336

8.4斷路337

8.5違反工藝原理338

8.6漏標342

8.7元件參數錯誤343

參考文獻345

書摘插畫

--------------------------------------------------------------------------------

【晶片製造電晶體工藝與設備】

內容簡介

《芯片制造:半導體工藝與設備》著重介紹了電晶體製造設備,並從實踐的角度出發,選取了具有代表性的設備進行講解。 為了讓讀者加深對各種設備用途的理解,採用了一邊闡述電晶體製造工藝流程、一邊說明各制造技術中所使用的製造設備及其結構和原理的講解管道,力求使讀者能够系統性地瞭解整個電晶體制造的體系。

《芯片制造:半導體工藝與設備》可作為從事集成電路工藝與設備方面工作的工程技術人員,以及相關研究人員的參攷用書,也可作為高等院校微電子、集成電路相關專業的規劃教材和教輔用書。

作者簡介

陳譯,副教授,男,廈門理工學院,獲得日本國立琉球大學電力電子工學專業博士學位,廈門市雙百人才,於2010年4月進入日本三墾電力株式會社,從事功率半導體器件(IGBT、MOSFET、SiC SBD、SiC MOSFET)的研發與產業化,經歷了先進功率半導體產業和科技發展的重要過程, 參與或領導團隊研發了30個品種以上的功率器件並實現產業化。 其主持研製的IGBT、MOSFET晶片已賣出數百萬片(其中IGBT晶片主要供貨給格力電器),總產值超過20億日元。 截止目前,擁有授權和受理發明專利50餘項,實用新型10餘項,發表科研論文15篇。 在面向工業和車規級的高端功率器件研發及量產方面經驗豐富,尤其擅長高端IGBT、Split-gate MOSFET、SiC功率器件的研究。

主要成果:

1)發明新型結構溝槽肖特基二極體,綜合性能比市面通用量產產品高出20%,並申報多項日本發明專利;

2)設計完成基於第六代溝槽場終止型(Field Stop)IGBT,並實現批量生產;

3)設計完成深槽分裂栅結構IGBT,綜合效能領先於現時國際*高水准並實現工程流片成功;

4)主持完成豐田汽車高可靠性車載應用功率MOSFET設計和製造;

5)設計開發1200V級SiC MOSFET器件並實現工程流片成功。

上述均屬於國內開創性或者領先水準的成果,綜合效能達到甚至領先於國際同類產品,具有巨大的科技和商業價值。

目錄

第1章導論1

1.1集成電路的發展歷史1

1.1.1世界上第一個集成電路1

1.1.2摩爾定律5

1.1.3集成電路的產業發展規律與節點7

1.1.4摩爾定律的終結或超摩爾時代11

1.2集成電路產業的發展15

1.2.1集成電路產業鏈15

1.2.2晶圓代工17

1.2.3集成電路產業結構變遷17

參考文獻20

第2章集成電路制造技術及生產線22

2.1集成電路製造技術22

2.1.1晶片製造22

2.1.2工藝劃分25

2.1.3工藝技術路線25

2.2集成電路生產線發展的歷程與設計27

2.2.1國外集成電路生產線發展情況27

2.2.2國內集成電路生產線發展情況29

2.2.3集成電路生產線的工藝設計30

2.3集成電路生產線的潔淨系統32

2.3.1潔淨室系統32

2.3.2空調系統33

2.3.3迴圈冷卻水系統35

2.3.4真空系統36

2.3.5排氣系統37

2.4集成電路生產線的發展趨勢38

參考文獻39

第3章晶圓製備與加工41

3.1簡介41

3.2矽材料42

3.2.1為什麼使用矽材料42

3.2.2晶體結構與晶向42

3.3晶圓製備44

3.3.1直拉法與直拉單晶爐45

3.3.2區熔法與區熔單晶爐46

3.4晶圓加工與設備48

3.4.1滾磨49

3.4.2切斷50

3.4.3切片51

3.4.4矽片退火54

3.4.5倒角55

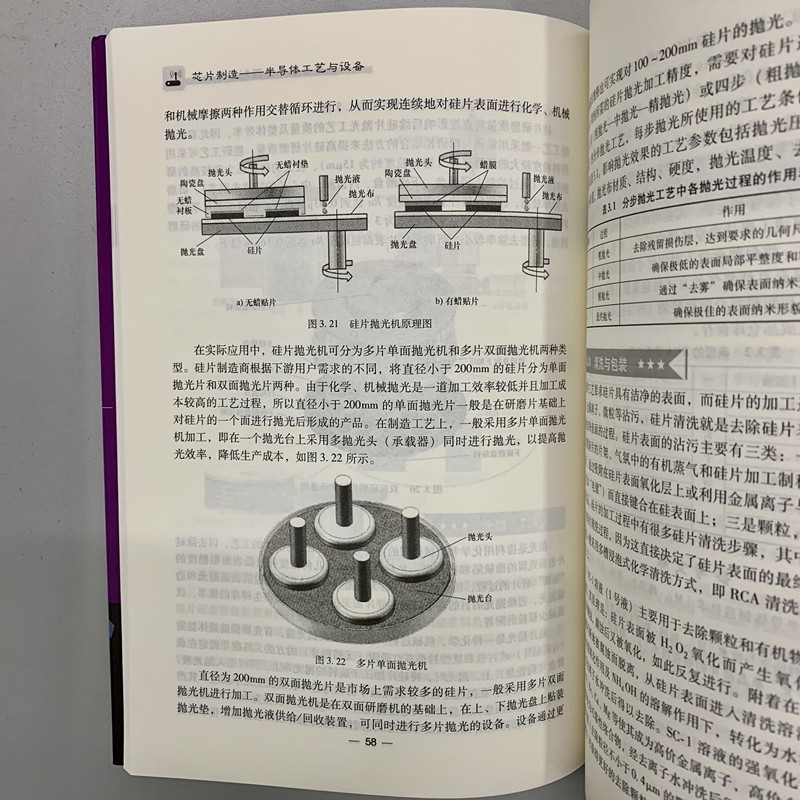

3.4.6研磨55

3.4.7拋光57

3.4.8清洗與包裝59

參考文獻60

第4章加熱工藝與設備61

4.1簡介61

4.2加熱單項工藝62

4.2.1氧化工藝62

4.2.2擴散工藝64

4.2.3退火工藝65

4.3加熱工藝的硬體設備66

4.3.1擴散設備66

4.3.2高壓氧化爐69

4.3.3快速退火處理設備70

參考文獻73

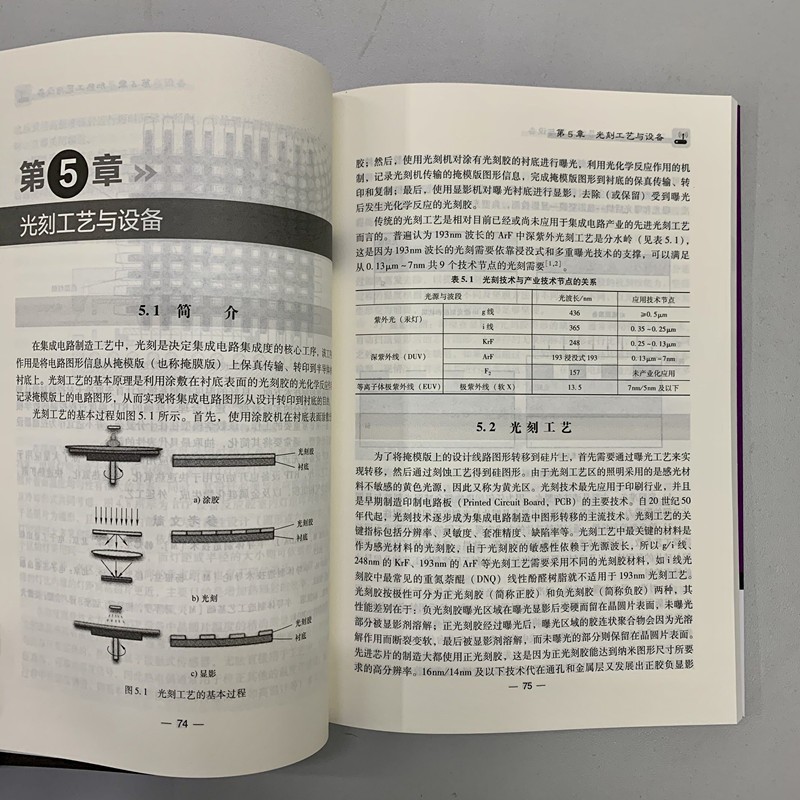

第5章光刻工藝與設備74

5.1簡介74

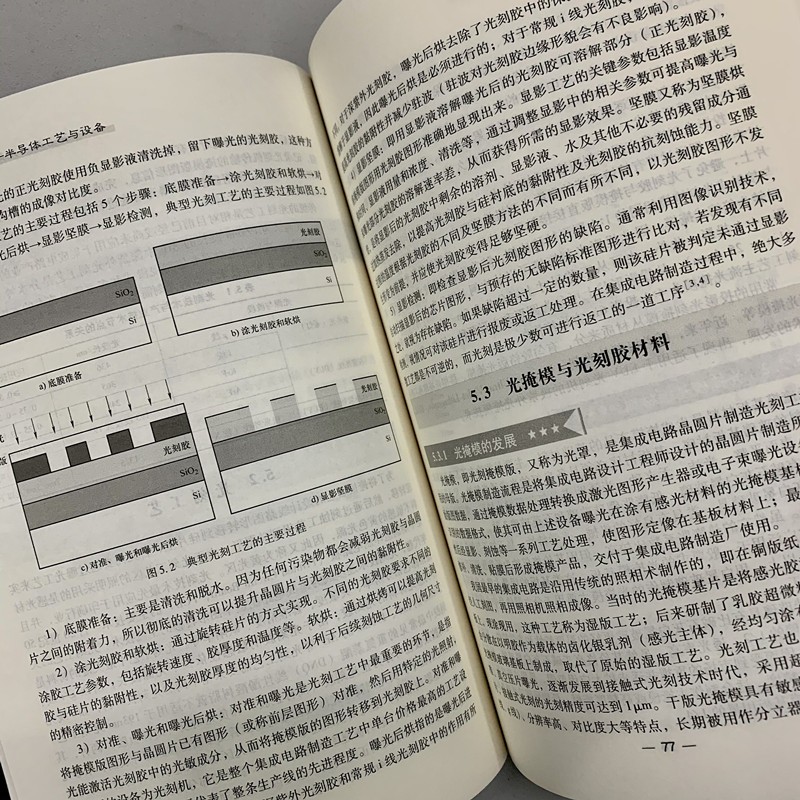

5.2光刻工藝75

5.3光掩模與光刻膠資料77

5.3.1光掩模的發展77

5.3.2光掩模基板資料78

5.3.3勻膠鉻版光掩模79

5.3.4移相光掩模80

5.3.5極紫外光掩模81

5.3.6光刻膠82

5.3.7光刻膠配套試劑83

5.4光刻設備84

5.4.1光刻技術的發展歷程84

5.4.2接觸/接近式光刻機86

5.4.3步進重複光刻機87

5.4.4步進掃描光刻機89

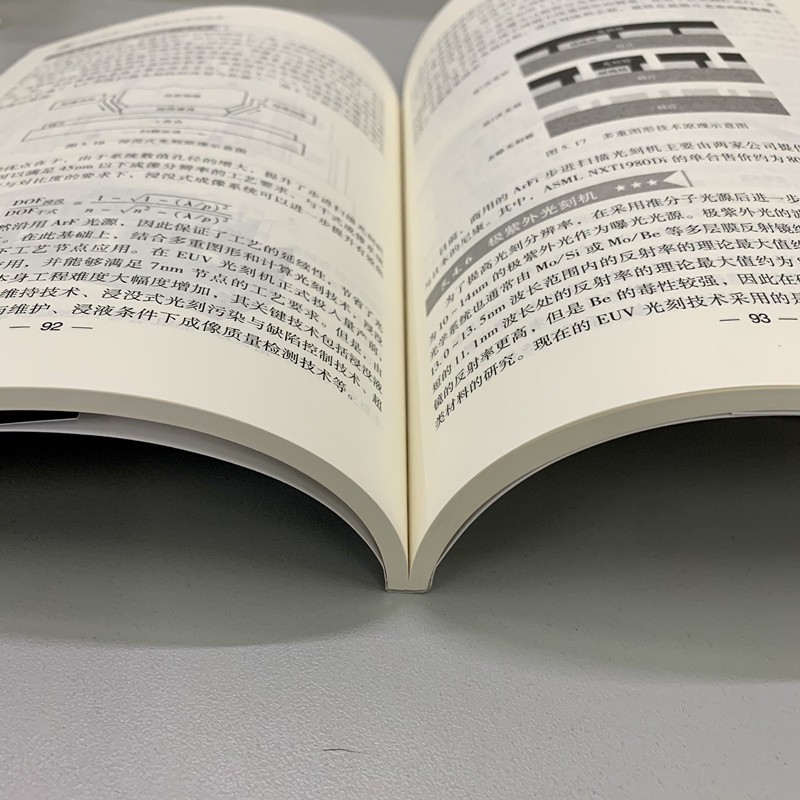

5.4.5浸沒式光刻機92

5.4.6極紫外光刻機93

5.4.7電子束光刻系統95

5.4.8納米電子束直寫系統96

5.4.9晶圓片勻膠顯影設備98

5.4.10濕法去膠系統101

參考文獻103

第6章刻蝕工藝及設備105

6.1簡介105

6.2刻蝕工藝106

6.2.1濕法刻蝕和清洗106

6.2.2幹法刻蝕和清洗108

6.3濕法刻蝕與清洗設備110

6.3.1槽式晶圓片清洗機110

6.3.2槽式晶圓片刻蝕機112

6.3.3單晶圓片濕法設備113

6.3.4單晶圓片清洗設備114

6.3.5單晶圓片刻蝕設備116

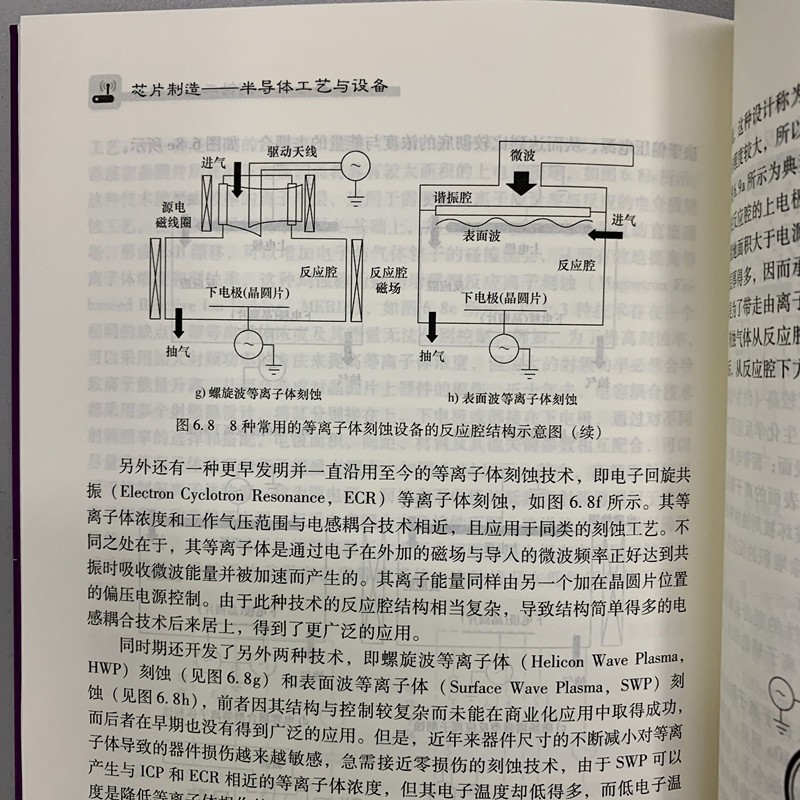

6.4幹法刻蝕設備117

6.4.1电浆刻蝕設備的分類117

6.4.2电浆刻蝕設備120

6.4.3反應離子刻蝕設備122

6.4.4磁場增强反應離子刻蝕設備123

6.4.5電容耦合电浆刻蝕設備125

6.4.6電感耦合电浆刻蝕設備127

參考文獻129

第7章離子注入工藝及設備131

7.1簡介131

7.2離子注入工藝132

7.2.1基本原理132

7.2.2離子注入主要參數135

7.3離子注入設備137

7.3.1基本結構137

7.3.2設備技術指標145

7.4損傷修復148

參考文獻148

第8章薄膜生長工藝及設備149

8.1簡介149

8.2薄膜生長工藝151

8.2.1物理氣相沉積及濺射工藝151

8.2.2化學氣相沉積工藝152

8.2.3原子層沉積工藝152

8.2.4外延工藝154

8.3薄膜生長設備154

8.3.1真空蒸鍍設備154

8.3.2直流物理氣相沉積設備156

8.3.3射頻物理氣相沉積設備158

8.3.4磁控濺射設備159

8.3.5離子化物理氣相沉積設備161

8.3.6常壓化學氣相沉積設備163

8.3.7低壓化學氣相沉積設備164

8.3.8电浆增强化學氣相沉積設備164

8.3.9原子層沉積設備165

8.3.10分子束外延系統167

8.3.11氣相外延系統168

8.3.12液相外延系統169

參考文獻171

第9章封裝工藝及設備172

9.1簡介172

9.2晶片級封裝173

9.2.1圓片减薄機173

9.2.2砂輪劃片機174

9.2.3雷射劃片機178

9.3元器件級封裝181

9.3.1粘片機181

9.3.2引線鍵合機182

9.4板卡級封裝185

9.4.1塑封機185

9.4.2電鍍及浸焊生產線186

9.4.3切筋成型機187

9.4.4鐳射列印設備187

參考文獻188

書摘插畫

新北趙**[0956***380]

7分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(四册)價:3150

臺南楊**[0986***368]

半小時前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】(兩册)價:1950

新竹陳**[0988***808]

2分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(兩册)價:1880

新北符**[0918***937]

15分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】(兩册)價:1950

高雄王**[0968***151]

15分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】(兩册)價:1950

桃園黃**[0918***955]

5分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(四册)價:3150

臺南劉**[0966***337]

7分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(兩册)價:1880

桃園孫**[0960***662]

11分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(四册)價:3150

臺南謝**[0968***381]

12分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】(兩册)價:1950

新竹陳**[0946***599]

5分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(兩册)價:1880

新北趙**[0966***488]

15分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(四册)價:3150

新北錢**[0938***343]

4分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】(兩册)價:1950

臺北趙**[0918***348]

7分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(兩册)價:1880

基隆王**[0938***977]

4分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】(兩册)價:1950

基隆柳**[0946***283]

12分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】(兩册)價:1950

臺北李**[0960***971]

4分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(四册)價:3150

嘉義黃**[0951***921]

7分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(兩册)價:1880

高雄符**[0933***202]

25分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(四册)價:3150

桃園劉**[0938***219]

25分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(兩册)價:1880

基隆李**[0920***178]

5分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(兩册)價:1880

桃園趙**[0933***882]

2分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】(兩册)價:1950

新北朱**[0966***845]

12分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(兩册)價:1880

桃園劉**[0946***788]

25分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(四册)價:3150

臺中趙**[0998***645]

12分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】(兩册)價:1950

基隆孫**[0951***656]

15分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(兩册)價:1880

嘉義劉**[0988***803]

11分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(兩册)價:1880

高雄李**[0932***948]

25分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(兩册)價:1880

新竹張**[0918***866]

12分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】(兩册)價:1950

新北鄭**[0986***655]

12分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(兩册)價:1880

臺中趙**[0920***913]

11分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(兩册)價:1880

嘉義王**[0988***964]

2分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(兩册)價:1880

基隆楊**[0960***918]

7分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(兩册)價:1880

臺南趙**[0933***656]

20分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(四册)價:3150

臺中鄭**[0920***148]

半小時前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(兩册)價:1880

新竹鍾**[0920***557]

5分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(四册)價:3150

高雄黃**[0988***147]

25分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】(兩册)價:1950

高雄王**[0938***675]

20分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(兩册)價:1880

臺中周**[0951***371]

20分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】(兩册)價:1950

臺北趙**[0986***382]

12分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】(兩册)價:1950

臺北朱**[0988***681]

20分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(四册)價:3150

基隆仲**[0918***456]

25分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(四册)價:3150

臺南黃**[0968***614]

4分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】(兩册)價:1950

嘉義鍾**[0960***105]

7分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(兩册)價:1880

臺北錢**[0956***362]

5分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】(兩册)價:1950

桃園方**[0998***723]

4分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】(兩册)價:1950

臺中張**[0998***853]

11分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(四册)價:3150

高雄趙**[0946***945]

20分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】(兩册)價:1950

臺中楊**[0932***134]

11分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(四册)價:3150

新竹王**[0988***963]

12分鐘前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】(四册)價:3150

基隆方**[0946***581]

半小時前【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】 - 【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】(兩册)價:1950